Мазмуну:

- 1-кадам: PWM модулун куруу- Булак файлы

- 2-кадам: PWM модулун куруу- Vivado орнотуусу

- 3-кадам: PWM модулун куруу- Долбоордун файлын түзүү

- 4-кадам: PWM модулун куруу

- 5-кадам: PWM модулун куруу

- 6-кадам: PWM модулун куруу

- 7-кадам: PWM модулун куруу

- 8-кадам: PWM модулун куруу

- 9-кадам: PWM модулун куруу- Аппараттык орнотуу

- 10-кадам: PWM модулун куруу- Bitstream түзүү жана SDKди ишке киргизүү

- 11-кадам: PWM модулун куруу- Xilinx SDKде жаңы тиркеме түзүңүз

- 12-кадам: PWM модулун куруу- Project Explorerге сереп (I)

- 13-кадам: PWM модулун куруу- Project Explorerге сереп (II)

- 14-кадам: PWM модулун куруу- Project Explorerдин обзору (III)

- 15-кадам: PWM модулун куруу- PWM функциясын ороо (I)

- 16-кадам: PWM модулун куруу- PWM функциясын ороп салуу (II)

- 17-кадам: PWM модулун куруу- PWM функциясын ороп алуу (III)

- 18-кадам: PWM модулун куруу- Аны иштетиңиз

- 19 -кадам: OV7670 менен Digilent ZYBOдо видео иштетүү

- 20 -кадам: Блок диаграммасын толуктаңыз

- 21 -кадам: OV7670ти ZYBOго туташтырыңыз

- 22 -кадам: Блок дизайнын түзүңүз

- 23 -кадам: OV7670 камерасын көзөмөлдөө жана тартуу үчүн VHDL файлдарын кошуңуз

- 24 -кадам: Чектөөлөр файлын кошуңуз

- 25 -кадам: HLS IP үчүн IP Repo кошуу

- 26 -кадам: Модулдарды жана IP кошуу

- 27 -кадам: IP конфигурациясынын жөндөөлөрү

- 28 -кадам: PS IP блогун кошуу жана конфигурациялоо

- 29 -кадам: 1 -бөлүк. Servo Motors үчүн PWM модулун куруу

- 30 -кадам: Video Input Side Connections (aclk Highlighted)

- 31 -кадам: OV7670 менен туташуулар

- 32 -кадам: Видеонун сыртындагы туташуулар

- 33 -кадам: Блокту жана туташууну автоматташтыруу

- 34 -кадам: HDL орогучту жаратыңыз

- 35 -кадам: Bitstream түзүү, SDKга жабдыктарды экспорттоо, Vivadodan SDKти иштетүү

- 36 -кадам: SDK (FreeRTOS жок)

- 37 -кадам: FreeRTOSту ишке ашыруу

- 38 -кадам: Колдонуу инструкциясы

- 39 -кадам: Шилтемелер жана шилтемелер

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 10:42.

- Акыркы өзгөртүү 2025-01-23 14:53.

Жөн эле 2-октук сервопроводдук PWM контроллерин түзүү боюнча деталдар үчүн биринчи кадамдан баштаңыз.

Толук долбоор үчүн массалык блок -схемадан баштаңыз (19 -кадам).

Биз колдонгон Camera + Pan/tilt орнотуусу:

Серверлерди туташтыруу үчүн Digilentтен PmodCON3 колдонулган.

1-кадам: PWM модулун куруу- Булак файлы

2-кадам: PWM модулун куруу- Vivado орнотуусу

Биринчиден, Vivado Design Suite Xilinx сайтынан жүктөп алыңыз. Бардык дизайн топтомун, анын ичинде Vivado Software Development Kit (SDK) орнотуңуз. Бул долбоор 2017.2 версиясын колдонот.

Бул арада Digilent Adept 2 Zybo платасынын драйвери катары да орнотулушу керек.

3-кадам: PWM модулун куруу- Долбоордун файлын түзүү

Долбоор файлын түзүүдөн мурун, бул жерде үйрөткүч катары Zybo файлын туура орнотконуңузга ишенишиңиз керек:

Vivado Version 2015.1 жана кийинчерээк Board File Орнотуу

Open Vivado 2017.2. Ыкчам баштоодо, Долбоор түзүү -> Кийинки -> Долбоордун аталышын (Долбооруңуздун атын ушул жерге коюңуз) -> Долбоордун Түрүн чыкылдатыңыз. Долбоордун түрүндө RTL долбоорун тандап, "Учурда булактарды көрсөтпө" дегенди белгилеңиз. Андан кийин, Демейки бөлүк үчүн "Такта" жана "Зибо" дисплейдин аты катары тандаңыз. Кийинки, Долбоорду баштоо үчүн Аяктоо дегенди басыңыз.

4-кадам: PWM модулун куруу

Flow Navigatorда "" Блок дизайнын түзүү "баскычын чыкылдатыңыз, андан кийин ОК басыңыз. керектүү IP кошуу үчүн "+" белгисин басыңыз. Кошуу:

- Бир ZYNQ7 иштетүү системасы эки AXI таймер

- Эки AXI таймер

5-кадам: PWM модулун куруу

IP кошкондон кийин, Блокту автоматташтыруу жана туташууну автоматташтыруу. Автоматташтыруу аяктагандан кийин, "axi_timer_0" блогунда pwm0 -> Тышкы кылуу оң баскычын чыкылдатыңыз. Pwm0 тышкы пинге pwm_Xaxis деп ат коюңуз. Ошондой эле, "axi_timer_1" блогунда жогорудагы процессти кайталап, pwm0 тышкы пинге pwm_Zaxis деп ат коюңуз.

6-кадам: PWM модулун куруу

Байкасаңыз, биз Vivado'догу Блок Дизайнын бүтүргөндө, HDL орогучту түзүшүбүз керек. Бул ар бир долбоор үчүн эң жогорку деңгээлдеги модуль болгондуктан.

7-кадам: PWM модулун куруу

Эми, биз блок -схемага байланышкан казыктарды дайындоо үчүн чектөө файлын орнотушубуз керек. Блок Дизайн терезесин жабыңыз, Булактар боюнча, "Булактарды кошуу"-> Чектөөлөрдү кошуу же түзүү-> Zybo-Master.xdcди биздин чектөө файлдары катары кошуу.

8-кадам: PWM модулун куруу

Чектөөлөр папкасынан Zybo-Master.xdc чектөө файлын ачыңыз, биз чыгаруу сигналдары катары белгилегибиз келген портторго комментарий бербеңиз жана "get_ports {XXXX}" деп аталышын өзгөртүңүз, ал XXXX Блок диаграммасында аталган тышкы пинди билдирет. Чектөө файлынын жөндөөсү сүрөттө көрсөтүлгөн.

9-кадам: PWM модулун куруу- Аппараттык орнотуу

Серво моторлорун Pmod CON3 менен туташтырыңыз. TowerPro SG90 - бул долбоордо биз колдонгон servo мотор модели. Серво моторунун зымдары үчүн кызгылт сары зым Pmod CON3төгү SIG пинге туташкан PWM сигналын билдирет. Кызыл зым Vcc - бул Pmod CON3төгү VS пинге туташкан электр зымы. Акырында, күрөң зым Gnd - GND пинине туташкан жер зымы. Андан кийин, Pmod CON3'ти Zybo Boardтун JD портунун жогорку катарына салыңыз.

10-кадам: PWM модулун куруу- Bitstream түзүү жана SDKди ишке киргизүү

1. Project Navigator өтмөгүндө BitStream генерациясын иштетүү.

2. Экспорттук жабдыктар: Файл> Экспорт> Аппаратты экспорттоо-> "bitstream камтыйт"-> OK 3. Launch SDK: File-> SDKти иштетүү.

11-кадам: PWM модулун куруу- Xilinx SDKде жаңы тиркеме түзүңүз

Жаңы колдонмо түзүү:

Файл> Жаңы> Колдонмо долбоору -> Долбооруңуздун атын киргизиңиз -> Аяктоо

Project Explorer астында үч папка болушу керек.

Бул учурда, "design_1_wrapper_hw_platform_0" мурун Vivado тарабынан экспорттолгон папка. Axis_2_PWM_SDK_bsp - бул тактаны колдоо пакети папкасы. Жана Axis_2_PWM_SDK - бул биздин негизги SDK долбоорубуздун папкасы. Axis_2_PWM_SDK "src" папкасынын астынан "helloworld.c" файлын көрө аласыз, мында "helloworld.c" негизги файл.

12-кадам: PWM модулун куруу- Project Explorerге сереп (I)

Project Explorer астындагы айрым файлдарды текшерип көрөлү. Биринчиден, "design_1_wrapper_hw_platform_0" папкасында "system.hdf" ачыңыз. Бул файл ps7_cortex9 процессорунун дареги картасын жана биздин дизайнда бар IP блокторун көрсөтөт.

13-кадам: PWM модулун куруу- Project Explorerге сереп (II)

Андан кийин, "Axis_2_PWM_SDK_bsp" папкасынын астындагы "кошуу" жана "libsrc" файлын текшериңиз. Бул жердеги китепкана файлдары бизге регистрлерди "ойнотпостон" аппараттык перифериялык жабдуулар менен иштешүүгө мүмкүнчүлүк берет.

14-кадам: PWM модулун куруу- Project Explorerдин обзору (III)

BSP документтери аркылуу xtmrctr.h AXI Timer менен байланышкан Xilinx Timer Control Library деп табылган. Адатта, биз каалаган PWM функциясын бул жерден таба алмакпыз. Бирок, эгер сиз "tmrctr_v4_3" документтерин окусаңыз, анда айдоочу учурда PWM ишин колдобой турганын көрсөтөт. PWM функциясынын жетишсиздигинен улам, биз xtmrctr.h жана AXI Timer v2.0 LogiCORE IP Продукт Колдонмосунун жардамы менен PWM функциябызды бүтүрүшүбүз керек.

15-кадам: PWM модулун куруу- PWM функциясын ороо (I)

"Helloworld.c" негизги файлына кайтып келүү үчүн, төмөнкү файл файлдарын камтыңыз:

16-кадам: PWM модулун куруу- PWM функциясын ороп салуу (II)

"Xparameters.h" аркылуу эки AXI TImerдин негизги даректерин аныктаңыз.

17-кадам: PWM модулун куруу- PWM функциясын ороп алуу (III)

Каалаган PWM функциясын куруңуз.

Duty_val: даражанын маанисин милдет циклине айландырат. Саат мезгили да дайындалышы керек.

PWM_START: PWM регистринин дарегин дайындоо жана PWM түзүүнү баштоо.

PWM_STOP: PWM регистр дарегин дайындоо жана PWM түзүүнү токтотуу.

Калган демо код "helloworld.c" "Axis_2_PWM_SDK" астында көрсөтүлгөн

18-кадам: PWM модулун куруу- Аны иштетиңиз

1. SDK аркылуу FPGA программасы

- USB порт аркылуу Zybo Boardту компьютерге туташтырыңыз.

- Xilinx Tools -> FPGA программасы

2. Программаны иштетүү

"Иштетүү" сүрөтчөсүн чыкылдатып, менюну түшүрүңүз -> Башкача иштетүү -> Аппараттык камсыздоодо ишке киргизүү

3. SDK терминалы

- SDK терминалын ачыңыз -> Сериялык портко туташуу -> OK

- Программаны иштетүү. Эгерде демо код ийгиликтүү иштесе, анда "Инициализация жасалды!" Көрүшүңүз керек. SDK терминалында.

19 -кадам: OV7670 менен Digilent ZYBOдо видео иштетүү

Толук архивдик файл тиркелди.

20 -кадам: Блок диаграммасын толуктаңыз

Бул долбоордун бардык байланыштарынын жана IP блокторунун толук диаграммасын көрсөтөт

21 -кадам: OV7670ти ZYBOго туташтырыңыз

Ov7670 модулун ZYBO Pmodsко туташтыруу үчүн байланыш түзүңүз

Маалымат Pmod - бул Pmod D

Control Pmod - бул Pmod C

Кошумча, PmodCON3 менен серверлерди бул окуу куралынын биринчи жарымында көрсөтүлгөндөй туташтырыңыз

22 -кадам: Блок дизайнын түзүңүз

Flow Navigator'да "Блок дизайнын түзүү" баскычын чыкылдатыңыз, андан кийин OK басыңыз.

23 -кадам: OV7670 камерасын көзөмөлдөө жана тартуу үчүн VHDL файлдарын кошуңуз

Бул кадамга тиркелген VHDL файлдарын долбоорго кошуңуз

24 -кадам: Чектөөлөр файлын кошуңуз

Тиркелген чектөөлөр файлын долбооруңузга кошуңуз.

25 -кадам: HLS IP үчүн IP Repo кошуу

Тиркелген Zip файлын алыңыз жана "HLS_repo" деп аталган жаңы каталогго (папкага) окшош жаңы папкага чыгарыңыз.

IP каталогуна өтүп, "Репозиторийди кошуу …" баскычын оң баскыч менен чыкылдатып, долбооруңузга IP кампасын кошуңуз.

Сиздин "HLS_repo" каталогуна өтүңүз жана аны тандаңыз.

Кошумча: HLS видео иштетүү блогун өзүңүз үчүн түзүңүз!

26 -кадам: Модулдарды жана IP кошуу

Ov7670_axi_stream_capture, debounce жана ov7670_controller модулдарын фон диаграммасына кошуу үчүн фонду оң баскыч менен чыкылдатып, "Модул кошуу…"

Ошо сыяктуу эле, IP кошуу:

- HLS_Video_Track

- Video Frame Buffer жазуу

- Video Frame Buffer окуу

- Видео Убакыт көзөмөлдөөчүсү

- AXI4-Stream Video Out үчүн

- 3 "Slice"

- Туруктуу

- AXI таймеринин 2

27 -кадам: IP конфигурациясынын жөндөөлөрү

Сүрөттөрдө көрсөтүлгөндөй

28 -кадам: PS IP блогун кошуу жана конфигурациялоо

ZYNQ7 иштетүү системасын блок -схемага кошуңуз

конфигурацияны түзөтүү:

-

PS-PL конфигурациясы

-

HP

- S HP 0 иштетүү

- S HP 1 иштетүү

-

-

Сааттын конфигурациясы

-

PL кездеме сааттары

- FCLK_0 100 МГцте

- FCLK_1 25 МГцте (OutputClock)

- FLCK_2 35 МГцте (<= 50 МГц) (CameraClock)

-

29 -кадам: 1 -бөлүк. Servo Motors үчүн PWM модулун куруу

Axi_timer_0 pwm0 жаңы pwm_Xaxis портуна алып келиңиз

Pwm_Zaxis жаңы чыгаруу портуна axi_timer_1 pwm0 алып келиңиз

30 -кадам: Video Input Side Connections (aclk Highlighted)

Видео кирүүчү тараптын IP блокторун туура туташтырыңыз

(* бул байланыштар автоматташтыруу учурунда туура опцияларды тандоо аркылуу түзүлүшү керек) axi_stream_capture тартып "aclk" барат:

- ap_clk видео кадр буферинде жазуу

- ap_clk HLS видео агымын иштетүү блогунда

- *Video Frame Буферинен AXI smartconnect IP боюнча aclk S_AXI_HP0 жазыңыз

- *HLS видео иштетүү блогунун S_AXI каналдары үчүн AXI Interconnect IP каналдарына туура келген aclk жана PS кадрына S_AXI_HP0_ACLK жазуу.

Видео агымынын сигналы жөн эле басып алуу блогунан Zynq эс тутумуна туташкан.

- Видео тартуу блогунан HLS иштетүү блогуна өтөт.

- HLS блогунан иштетилген видео кадр буферине жазуу блогуна барат.

- *Кадрдык буфердик жазуу блогу Zynq PS блогундагы HP0 интерфейсине туташат.

- Тартуу блогунун m_axis_tuser сигналы HLS иштетүү блогундагы video_in_TUSER киргизүү сигналына жана ошол эле блоктогу ap_start сигналына кол менен өткөрүлөт.

TUSER (tuser) сигналы AXI видео агымы протоколу менен видеонун кадрынын башталышын көрсөтүү үчүн колдонулат. AP_Start HLS блогуна иштетүүнү баштоону айтат. бир автобустун бир сигналын туташтырып, ушул жол менен бөлгөндө, аны автобустун калган бөлүгүнүн кадимки токтотуу чекитине туташтыруу керек. Vivado, эгер сиз сигналды кол менен туташтырсаңыз, ал кадимкидей туташып турган нерсени ажыраткыңыз келет деп болжойт.

IP блокторунун конфигурация орнотуулары:

Видео кадр буферин жазыңыз:

Видео форматтары: RGB8

Саатына 1 үлгү Макс мамычалар: 1280 (> = 640) Максималдуу саптар: 960 (> = 480) Максималдуу маалымат туурасы: 8

31 -кадам: OV7670 менен туташуулар

Ov7670_axi_stream_capture блогунда

- Бардык киргизүүлөрдү тышкы кылыңыз (пинге оң баскыч менен чыкылдатып, менюдан тандаңыз, же сол басуу-> ctrl+T)

- Аттарын кандай болсо, ошондой калтыргыла

Ov7670_controller блогунда

- Блоктун бардык чыгууларын тышкы кылыңыз

- Config_finished портунун атын led0 деп өзгөртүңүз

- clkти CameraClockко туташтыруу (<= 50MHz) (FCLK_2)

Чыгуу блогунда

- button1 киришин btn0 деп аталган тышкы киргизүү портуна туташтырыңыз

- out1ди ov7670_controller IP блогундагы кайра жөнөтүү линиясына туташтырыңыз

- button2 киришин btn3 деп аталган тышкы киргизүү портуна туташтырыңыз

- Out2nди процессор тутумундагы ext_reset_in киришине туташтыруу, видео тартуу саат домени үчүн IPти калыбына келтирүү. (*Бул IP түзүлгөндөн кийин жасалышы керек болушу мүмкүн*)

- clkти CameraClockко туташтыруу (<= 50MHz) (FCLK_2)

32 -кадам: Видеонун сыртындагы туташуулар

Блоктор үчүн Video Timing Controller (VTC), AXI4-Stream to Video Out жана кесимдер

- Vid_io_out_clk жана VTC clk үчүн 25MHz саатты (FCLK_1) колдонуңуз

- AXI4-Streamдеги Video Out үчүн aclk үчүн 100MHz саатты (FCLK_0) колдонуңуз

- vtiming_out to vtiming_in

- Video Frame Buffer окуу m_axis_video AXI4-Stream'ге Video Out to video_in өтөт

- vtg_ce gen_clken ге барат

- VTC clken, aclken, vid_io_out_ce'ди Constant dout менен байланыштырыңыз [0: 0]

- Vid_hsync жана vid_vsyncти тиешелүү түрдө vga_hs жана vga_vs тышкы чыгаруу портторуна алып келиңиз. (сүрөттө жок)

Кесимдер:

-

Тилкелер тиркелген сүрөттөрдө көрсөтүлгөндөй орнотулушу керек

- блокторду slice_red, slice_green жана slice_blue деп атоо

- блоктун аталышы боюнча сүрөттөрдө көрсөтүлгөндөй тилкенин диапазону

- сүрөттө көрсөтүлгөндөй, ар бир тилкенин тышкы портуна туташтырыңыз.

- vid_data [23: 0] ар бир кесимдин киришине туташат (Din [23: 0])

33 -кадам: Блокту жана туташууну автоматташтыруу

ZYNQ7 PS блогундагы нерселерди туташтыруу үчүн Блокту Автоматташтырууну иштетүү. Сүрөттө көрсөтүлгөндөй.

Бардык туташуу IP түзүү үчүн Connection автоматташтырууну иштетүү. Ар бир сүрөттөгү бардык варианттарга жакшылап көңүл буруңуз.

Чыгуу блогунда, out2n видео тартуу саат доменине туташыңыз Процессор системасы ext_reset_in кирүүсүн калыбына келтирүү.

34 -кадам: HDL орогучту жаратыңыз

Блоктун дизайны үчүн HDL орогучту түзүңүз.

Аны жогорку модуль катары коюңуз.

35 -кадам: Bitstream түзүү, SDKга жабдыктарды экспорттоо, Vivadodan SDKти иштетүү

Экспортко бит агымын кошууну тактаңыз.

Bitstream генерациясы өтө көп убакытты алышы мүмкүн.

Андан кийин SDK иштетүү

36 -кадам: SDK (FreeRTOS жок)

Бул версия FreeRTOSту колдонбостон, кодду жакшылап тыгыздаштырат.

Аппараттык дизайнга негизделген өз алдынча BSP түзүңүз. Демейки параметрлер жакшы болушу керек. BSP булактары түзүлгөнүн текшериңиз.

Сүрөттө көрсөтүлгөндөй колдонмону түзүңүз. (бош колдонмо)

Автогенерацияланган негизги файлды жок кылып, тиркелген файлдарды импорттоңуз.

37 -кадам: FreeRTOSту ишке ашыруу

Бул версия FreeRTOSту колдонот. Аппараттык дизайнга негизделген FreeRTOS901 BSP түзүңүз. Демейки параметрлер жакшы болушу керек. BSP булактары түзүлгөнүн текшериңиз.

Сүрөттө көрсөтүлгөндөй колдонмону түзүңүз. (бош колдонмо)

Автогенерацияланган негизги файлды жок кылып, тиркелген файлдарды импорттоңуз.

38 -кадам: Колдонуу инструкциясы

Бул долбоорду ишке киргизүү бир аз татаал. Кадамдарды ирети менен аткарыңыз.

Сиздин ZYBO күйгүзүлгөндө эч нерсе өзү жүктөлбөй турганын текшериңиз. Бул Done LED күйбөшү керек дегенди билдирет. Мунун бир жолу - жүктөөчү булак секирүүчүсүн JTAGка коюу.

SDKдан программалагыңыз келген долбоорду ачыңыз (FreeRTOS же жок)

- ZYBOну күйгүзүңүз. Done LED күйбөшү керек.

- FPGAны бит файлы менен программалаңыз. Бүткөн LED күйүп турушу керек. Led0 күйбөшү керек.

- Кодду иштетиңиз (эгер сиз ушундай кылып жатсаңыз, баштапкы чекитти басып өтүүнү унутпаңыз).

Бул учурда сиз VGA дисплейиңизде бир жыйынтыкты алышыңыз керек.

Кайра баштоо үчүн (эгер мүчүлүштүктөр болсо же): PS-SRST баскычын тез таптап же ZYBOну өчүрүп, кайра күйгүзүңүз. 2 -кадамдан улантыңыз.

Мүчүлүштүктөрдү оңдоочу менен процессорду токтотуу Камераны жылдыруунун ордуна позицияны кармап турууга алып келет. Видео агымы баары бир улана берет.

39 -кадам: Шилтемелер жана шилтемелер

Xilinx маалымдама колдонмолору жана документтери:

- PG044 - AXI -Stream Video Out үчүн

- PG278 - Video Frame Буфери Окуу/Жазуу

Башка шилтемелер:

- Лауринин блогу - VDMA киргизүү

- Лауринин блогу - OV7670 BRAM аркылуу VGA өндүрүшүнө

- Hamsterworks вики, Майк Филдс, OV7670 кодунун баштапкы булагы

- Негизги убакыт өзгөчөлүктөрүн көрсөтүүчү маалыматтык таблица

Сунушталууда:

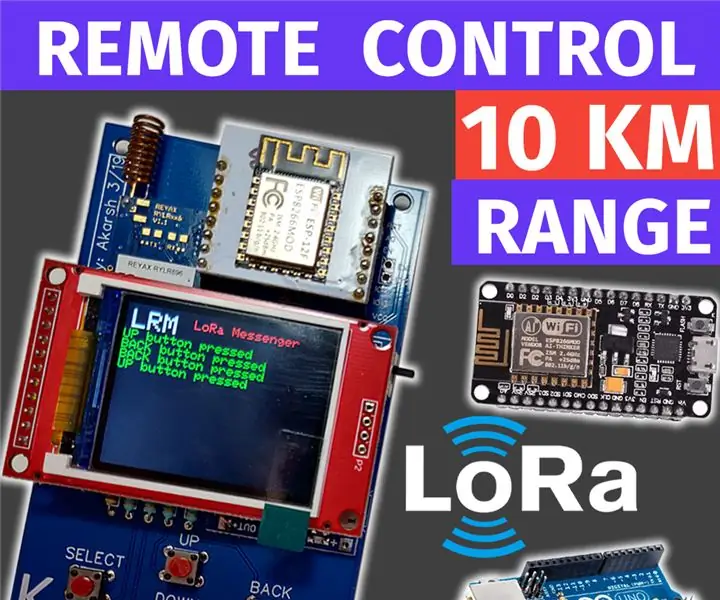

LoRa негизделген алыстан башкаруу - Чоң аралыктан башкаруу шаймандары: 8 кадам

LoRa негизделген алыстан башкаруу | Түзмөктөр чоң аралыктан: Эй, эмне болду, балдар! Akarsh бул жерде CETechтен. Бул долбоордо биз светодиоддор, моторлор сыяктуу ар кандай приборлорду көзөмөлдөө үчүн колдонула турган алыстан башкаруу пультун түзөбүз же эгерде биз күнүмдүк жашообуз жөнүндө айтсак, биз өзүбүздүн үй колдонуучубузду башкара алабыз

DSLR убакыттын өтүшү үчүн Пан жана Тент механизми: 7 кадам (Сүрөттөр менен)

DSLR Time Lapses үчүн Pan and Tilt механизми: Менде бир нече тепкичтүү моторлор бар болчу жана аларды чындап бир нерсе жасоо үчүн колдонууну кааладым. Мен DSLR камерам үчүн Pan and Tilt системасын жасайм деп чечтим, ошондо мен эң сонун убакытты таба алам. Сизге керектүү нерселер: 2x тепкичтүү моторлор -htt

Android Mobile менен RGB Камера Арткы Жарыкты башкаруу: 6 кадам

Android Mobile менен RGB Камера Арткы Жарыкты башкаруу: RGB Lights Compeding Three LED Lights Red, Green & Көк. Биз LEDдин жарыктыгын жөнгө салабыз, ал жаңы түс түзөт. Ошентип, Жарыктыкты LED коддору аркылуу тууралоо (0-255) .►ДИДдер бири-бирине абдан жакын болгондуктан, биз акыркы түстөрдү гана көрө алабыз

Blynk тиркемеси менен USB аркылуу смартфонду колдонуу менен Arduino башкаруу: 7 кадам (сүрөттөр менен)

Blynk тиркемеси менен USB аркылуу смартфонду колдонуу аркылуу Arduino башкаруу жөнөкөй чечим алыстан башкаруучу сиздин Arduino же c

Алыстан башкарылган пан жана эңкейиш башы: 7 кадам

Алыстан башкарылуучу пан жана эңкейиш башы: Мен ар дайым алыстан башкарылуучу көмөч менен башты эңкейгим келет. Балким, бул менин видеокамерам, резина тобу же суу тапанчасы үчүн болгон. Бул кичинекей долбоор менен үстүнкү палубага эмнени салганыңыздын мааниси жок (анча деле оор болбосо)