Мазмуну:

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 10:40.

- Акыркы өзгөртүү 2025-01-23 14:51.

Бул көрсөтмөдө биз SPH Bus Masterди нөлдөн баштап VHDLде иштеп чыгалы деп жатабыз.

1 -кадам: SPIге сереп

- SPI - синхрондуу сериялык автобус

- Анын популярдуулугу жана жөнөкөйлүгү аны сериялуу байланыштын де -факто стандарты кылды

- Толук дуплекстүү автобус

- Жөнөкөй протокол жана эң ылдам сериялык автобустардын бири

2 -кадам: Дизайн өзгөчөлүктөрү

Бул биз иштеп чыга турган SPI Masterдин өзгөчөлүктөрү:

- Иштин бардык төрт режимин колдойт; динамикалык конфигурацияланат

- Саат энергияны үнөмдөө үчүн көзөмөлдү иштетет

- Статикалык конфигурацияланган сөздүн узундугу жана ылдамдыгы

- Берүү жана кабыл алуу үчүн бирдиктүү үзгүлтүк

3 -кадам: өчүрүү

Биринчиден, биздин IP эки интерфейске ээ болушу керек. Бири сериялык интерфейс, экинчиси параллель интерфейс. Сериялык интерфейс SPIдин де-факто стандарттык сигналдарынан турат: MOSI, MISO, SS, SCLK.

MOSI кээде SDO деп аталат, ал эми MISO кээде SDI деп аталат.

Сериялык интерфейс тышкы перифериялык түзүлүштөр менен, башкача айтканда, SPI кулдары менен байланышуу үчүн колдонулат.

Параллелдүү интерфейс биздин хост менен байланышуу үчүн колдонулат, башкача айтканда. Микроконтроллер же микропроцессор, ал чындыгында Мастерге кандай маалыматтарды сериялык линиялар аркылуу сериялык түрдө берүү жана алуу керек экенин айтат. Башкача айтканда, бардык маалымат шиналары параллелдүү интерфейске таандык.

Бизде ички SPI логикасын, ошондой эле биз өзүбүз жараткан SCLKти башкарган глобалдык саат бар.

Бизде жазууну иштетүү, саатты иштетүү сыяктуу кээ бир башкаруу сигналдары бар. Жана үзгүлтүк жана башка абал сигналдары.

Биз татаал башкаруу шарттары менен күрөшүүгө туура келгендиктен, FSM сыяктуу сериялык байланыш IP -лерин иштеп чыгуу оңой. Биз SPI мастерин FSM катары да иштеп чыгабыз. FSM эки эсе SCLK башка ички саат менен башкарылат. Бул ички саат глобалдык сааттын синхрондуу эсептегичтеринин жардамы менен түзүлөт.

Саат аралык домендерди башкаруучу бардык сигналдар коопсуз тарапта болушу үчүн синхронизаторлорго ээ.

4 -кадам: SPL Master Core жана Simulation Waveforms RTL көрүнүшү

Бул эч кандай атайын FPGA IPи колдонулбаган жылаңач RTL дизайны. Демек, бул каалаган FPGAга толугу менен көчмө код.

Сунушталууда:

VHDLдеги жөнөкөй кэш контроллеринин дизайны: 4 кадам

VHDLдеги жөнөкөй кэш контроллеринин дизайны: Мен муну үйрөтүп жатам, анткени кээ бир VHDL коддорун үйрөнүү жана кэш контроллерин иштеп чыгууну баштоо кыйынга турду. Ошентип, мен нөлдөн баштап кэш контроллерин иштеп чыктым жана аны FPGAда ийгиликтүү сынап көрдүм. Менде п

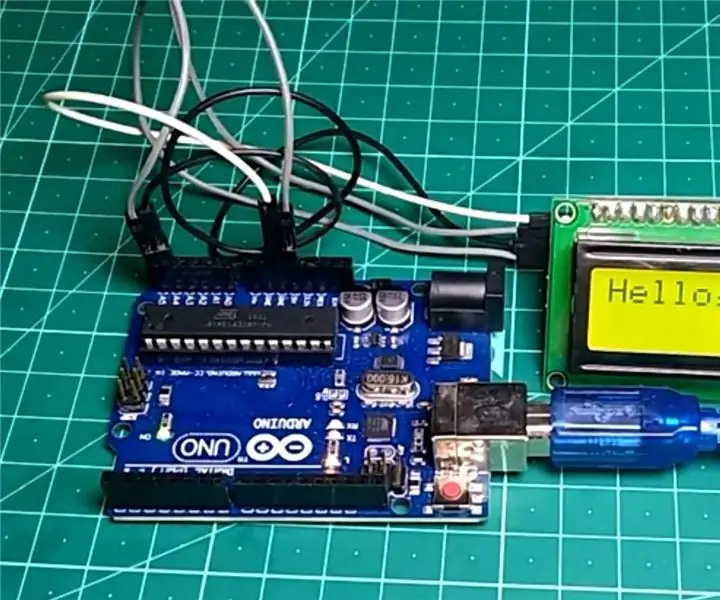

I2C / IIC ЖК дисплей - IUC LCD дисплейине SPI ЖКны колдонуңуз, Arduino менен IIC модулуна SPI колдонуңуз: 5 кадам

I2C / IIC ЖК дисплей | IUC LCD дисплейине SPI ЖК дисплейин колдонуңуз, SPIди IIC модулуна Arduino менен колдонуңуз: Салам балдар, анткени кадимки SPI LCD 1602де туташуу үчүн зымдар өтө көп болгондуктан, аны arduino менен иштетүү өтө кыйын, бирок базарда жеткиликтүү болгон бир модуль бар. SPI дисплейин IIC дисплейине айландырыңыз, ошондо сиз 4 зымды гана туташтырууңуз керек

VHDLдеги I2C Masterдин дизайны: 5 кадам

VHDLдеги I2C Masterдин дизайны: Бул көрсөтмөдө, VHDLде жөнөкөй I2C мастеринин дизайны талкууланат. ЭСКЕРТҮҮ: толук сүрөттү көрүү үчүн ар бир сүрөттү басыңыз

VHDLдеги UART дизайны: 5 кадам

VHDLдеги UART дизайны: UART универсалдуу асинхрондук кабыл алуучу өткөргүчтү билдирет. Бул эң популярдуу жана эң жөнөкөй сериялык байланыш протоколу. Бул көрсөтмөдө сиз VHDLде UART модулун кантип иштеп чыгууну үйрөнөсүз

VHDLдеги Mastermind Оюну: 3 кадам

VHDLдеги Mastermind Game: Биздин долбоор үчүн биз “ Mastermind ” VHDLдеги оюн Basys3 тактасында ойнотулат. Mastermind салттуу түрдө казык жана оюн тактасы менен ойнолуучу кодду бузуучу оюн. Бир оюнчу 4 катар катары менен түрдүү түстөгү казыктарды жайгаштырат