Мазмуну:

- 1 -кадам: Блок диаграммасы

- 2 -кадам: Иштөө принциби

- 3 -кадам: Логиканы ишке ашыруу

- 4 -кадам: Түйүндү чечүү

- 5 -кадам: Түзмөктүн конфигурациясы - Matrix0 Circuit

- 6 -кадам: Түзмөктүн конфигурациясы - SPI Clocking Logic

- 7 -кадам: Түзмөктүн конфигурациясы - Matrix0 компоненттеринин касиеттери

- 8 -кадам: Түзмөктүн конфигурациясы - Matrix1 Circuit

- 9 -кадам: Түзмөктүн конфигурациясы - 3 -бит бинардык эсептегич

- 10 -кадам: Түзмөктүн конфигурациясы - 3 -бит логиканы салыштыруу

- 11 -кадам: Түзмөктү конфигурациялоо - Санариптик логиканы жана убактылуу каттоону

- 12 -кадам: Түзмөктүн конфигурациясы - Matrix1 компоненттеринин касиеттери

- 13 -кадам: Жыйынтыктар

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 10:39.

- Акыркы өзгөртүү 2025-01-23 14:51.

Башкаруу тутумдары жана ага байланышкан түзмөктөр бир нече энергия булактары менен иштешет, мисалы, бир жактуу линиялар же батареялар, жана берилген топтомдун ичинен эң жогорку (же эң төмөнкү) линияны көзөмөлдөшү керек.

Мисалы, "көп батарея" кубаттуулугу бар системада жүктү которуштуруу системадан батарейканын массивиндеги минималдуу же максималдуу чыңалууну (белгилүү бир которуу алгоритминин функциясы катары максимум же мин) көзөмөлдөп турууну талап кылат жана жүктү динамикалык түрдө реалдуу убакытта эң ылайыктуу булак. Же болбосо, туура заряддоо үчүн системага эң төмөнкү чыңалуудагы батареяны убактылуу ажыратуу керек болушу мүмкүн.

Дагы бир мисал - бул күн батареяларынын заманбап системасы, анда ар бир күн панели тилтротат механизми менен жана күндү көзөмөлдөө схемасы менен жабдылган (экинчиси панелди багыттоо үчүн Күндүн абалы жөнүндө маалымат берет). Максималдуу чыңалуу маалыматы менен, күн панелинин ар бир позициясы чындыгында эң жогорку вольтту жеткирүүчү жип панелинин негизинде так жөнгө салынышы мүмкүн, ошону менен бийликти оптималдаштыруунун жогорку деңгээлине жетет.

Негизинен максималдуу чыңалуу жолдоочусун ишке ашыра ала турган коммерциялык ICлердин (негизинен микроконтроллерлердин) бир нече ар кандай маркалары бар. Бирок, алар программалоону талап кылат жана аралаш сигналдык чечимге караганда азыраак үнөмдүү. Dialog GreenPAKTM дизайнын толуктоо дизайндын жеткиликтүүлүгүнө, көлөмүнө жана модулдуулугуна оң таасирин тийгизет. Бул дизайн аналогдук жана санариптик схемаларды бир чипке интеграциялоонун пайдасын колдонот.

Бул Нускамада сегиз башка булактын арасынан максималдуу (же акырында мин) чыңалуу тапкычты ишке ашыруу үчүн керектүү аналогдук алдыңкы жана санариптик логика ишке ашырылат.

8 каналдуу аналогдук макс/мин чыңалуу мониторун ишке ашыруу үчүн SLG46620G колдонулат.

Төмөндө биз 8 каналдуу аналогдук максималдуу/мүн чыңалуу мониторун түзүү үчүн программанын кандайча чечилгенин түшүнүү үчүн керектүү кадамдарды сүрөттөдүк. Бирок, эгер сиз программалоонун жыйынтыгын алууну кааласаңыз, GreenPAK программасын жүктөп алыңыз, буга чейин бүткөн GreenPAK Дизайн Файлын көрүңүз. GreenPAK Development Kitти компьютериңизге сайыңыз жана 8 каналдуу аналогдук максималдуу/мүн чыңалуу мониторун түзүү үчүн программаны басыңыз.

1 -кадам: Блок диаграммасы

Figure 1 ишке киргизилген системанын глобалдык диаграммасын көрсөтөт.

8ге чейин өзгөрмөлүү чыңалуу булактары Multiplexed жана башкаларга карата эң жогорку чыңалуудагы булакты тандоого жөндөмдүү ички дизайнга туташкан GreenPAKтин ADC модулуна туташкан. Ички логика бул маалыматты көрсөтүү же андан ары иштетүү үчүн чыгарат.

Дизайн GreenPAK SLG46620G продуктуна негизделген, анткени ал тиркеме үчүн бардык керектүү аналогдук жана санариптик блокторду камтыйт. Бул ишке ашырууда массив түздөн -түз GreenPAK IC тарабынан башкарылган ADG508 аналогдук мультиплексорунун жардамы менен сканерленет.

Чыгуу маалыматы максималдуу чыңалуудагы чыңалуу булагынын номерине туура келген 3 биттик санариптик сан. Бул маалыматты алуунун түз жолу-бул 7 сегменттүү дисплей аркылуу номерди көрсөтүү. Бул SLG46620Gнин санариптик чыгарылышын 7-сегменттүү дисплей драйверине, мисалы Reference-де сүрөттөлгөн GreenPAK чечими же жалпы 74LS47 IC менен байланыштыруу аркылуу оңой эле ишке ашышы мүмкүн.

Берилген схема максималдуу чыңалууну издейт. Дизайнды минималдуу чыңалуу тапкычка айландыруу үчүн аналогдук мультиплексор менен GreenPAK аналогдук киришинин ортосуна мультиплексордун чыгышын 1 В чыңалуу чыңалуусунан алып салуу менен жөнөкөй алдын ала кондиционердик схеманы кошуу керек.

2 -кадам: Иштөө принциби

Дизайн максималдуу чыңалуудагы булакты тандап алууну көздөйт, ошондуктан акыркы максимумдун маанисин сактоодо жана аны кийинки киргизилген мааниси менен салыштырууда сканерлөө жүргүзүлөт (бул сканердеги кийинки чыңалуу булагына таандык).

Төмөндө биз "сканерлөө" же "укурук" катары бардык кириштер боюнча толук мультиплекстештирүү тизмегине кайрылабыз.

Эки баалуулукту салыштыруу ACMP компоненттеринин жардамы менен ишке ашпайт (бирок SLG46620Gде бар), тескерисинче, баалуулуктар тиешелүү түрдө санариптештирилгенден кийин DCMP модулу аркылуу. Бул биринчи жолу шилтемеде каралган өнүккөн жана тазаланган техника.

Figure 2 SLG46620G бул дизайн үчүн кандай структураланганын көрсөтөт.

Аналогдук кирүү сигналы 1 кирешеси бар PGA компоненти аркылуу ADC кирүүсүнө барат. Ар кандай киреше орнотуулары, кирүү чыңалуусун 0-1 Vге картага түшүрүү үчүн алдыңкы кондиционердик электроника менен мыкты матчты табууга да мүмкүн. GreenPAK ADC модулунун диапазону.

ADC бирдиктүү режимде иштейт жана аналогдук сигналды 8 биттик санариптик кодго айлантат, андан кийин DCMP модулуна өткөрүлөт. Санарип коду ADC/FSM Буфери катары конфигурацияланган SPI блогуна да берилет, мында санарип кодун кийинки импульс SPI CLK киришине келгенге чейин сактоого жана өзгөртүүгө болбойт. Белгиленгендей, атайын логикалык блок SPI CLK киргизүүнү башкарат. Бул бөлүктү кийинчерээк иликтейбиз, анткени бул туура иштеши үчүн жооп берген "негизги" логика. Жаңы санариптик код SPI модулуна сакталат, эгерде ал чыныгы кирүү чыңалуусуна таандык.

DCMP компоненти учурдагы ADC маалыматын SPI блогунда сакталган акыркы жеңүүчү менен (бул эң акыркы табылган максимум) салыштыруу үчүн колдонулат. Жаңы ADC маалыматы мурунку маалыматтан чоң болгондо, OUT+ чыгарылышында импульс пайда болот. Биз жаңы жеңүүчү менен SPI блогун жаңыртуу үчүн OUT+ сигналын колдонобуз.

Глобалдык саат сигналы ADC конверсиясын жана жалпы убакытты айдайт. Которуу жүргүзүлгөндөн кийин, ADC параллелдүү маалымат чыгаруу менен өз убагында координацияланган ADC INT сигналынын импульсу. Биз INT чыгымын Matrix1де DFFs тарабынан ишке ашырылган 3 биттик экилик эсептегичти көбөйтүү үчүн да колдонобуз, бул үч себептен пайдалуу:

1. Эсептегичтин чыгуу линиялары тышкы аналогдук мультиплексорго кайрылып, ошону менен кийинки кирүү чыңалуусун ADCге кызмат кылат;

2. Сканерлөө учурунда убактылуу жеңүүчүсүн сактоо үчүн эсептөө 3-бит реестрине (Matrix1де киргизилген) тоңдурулган;

3. Сканерлөө аяктагандан кийин эсептөө экинчи 3 биттик реестрди (Matrix0до ишке ашырылган) жаңыртуу үчүн декоддолгон.

3 -кадам: Логиканы ишке ашыруу

ADC модулу ырааттуу түрдө бардык киргизүү чыңалуусунун айландырылган маалыматын биринин артынан бирин чексиз камсыз кылат. Мультиплексорго 0b111 (ондук 7) кайрылганда, эсептегич 0b000ге (ондук 0) айланып, кирүү чыңалуусунун жаңы сканерин баштайт.

Скандоо учурунда, параллелдүү маалымат чыгаруу жарактуу болгондо, ADC INT чыгаруу сигналы пайда болот. Бул сигнал импульс болгондо, аналогдук мультиплексор PGAга тиешелүү чыңалуу менен камсыз кылып, кийинки кирүүгө өтүшү керек. Ошондуктан, ADC INT чыгышы 2-сүрөттөгү 3-бит бинардык эсептегичтин түз сааты болуп саналат, анын 3-бит параллелдүү чыгаруу сөзү тышкы аналогдук мультиплексорго түз кайрылат (1-сүрөттөгү “V тандоо”).

Келгиле, азыр кириш чыңалуусу төмөнкү байланыштарга ээ болушу керек болгон мисалга кайрылалы:

а) V0 <V1 <V2

б) V2> V3, V4

в) V5> V2

Figure 3 max-чечим механизмине катышкан негизги сигналдарды билдирет.

Маалыматтар акыры SPI буфердик реестрине INT импульсу менен синхрондуу түрдө киргендиктен, SPI буферинин мазмуну кийинки ADC конверсиясынын натыйжасы менен салыштырылган терезе бар. Бул өзгөчө убакыт DCMP өндүрүшүндө OUT+ импульстарынын пайда болушуна алып келет. Биз SPI буфердик реестрине жаңы баалуулуктарды жүктөө үчүн бул импульстардан пайдалана алабыз.

Мурунку Сүрөттөгү SPI буфердик маалымат линиясынан көрүнүп тургандай, SPI реестри дайыма 8 киргизүүнүн ичинен эң чоң маанини камтыйт жана ал DCMP модулу тарабынан чоңураак маани аныкталганда гана жаңыртылат (DCMPге шилтеме берүү менен) Участоктун OUT+ чыгаруу сызыгы, жок болгон импульстар V2дин V5 менен салыштырмалуу реестрде калуусуна себеп болот).

4 -кадам: Түйүндү чечүү

Эгерде ишке ашырылган логика жогоруда айтылгандай боло турган болсо, анда биз туюкка кептелет экенибиз анык: система SPI буфердик реестринде сакталгандан жогору болгон чыңалууларды гана аныктай алат.

Бул чыңалуу төмөндөп, андан кийин дагы бир кирүү эң жогорку болуп калат: ал эч качан аныкталбайт. Бул абал 4 -сүрөттө жакшыраак түшүндүрүлгөн. ачыктык.

2 кайталоо учурунда V3 төмөндөйт жана V1 чыныгы чыңалуу болуп саналат. Бирок DCMP модулу импульсту камсыз кылбайт, анткени SPI буфердик реестрине сакталган маалыматтар (0,6 Вге туура келет) V1ге (0,4 В) туура келгенден чоңураак.

Андан кийин система "абсолюттук" макс тапкыч катары иштейт жана чыгарууну туура жаңыртпайт.

Бул көйгөйдү жеңүүнүн эң жакшы жолу - бул система бардык каналдардын толук сурамжылоо циклин аяктагандан кийин, маалыматтарды SPI Буфер Реестрине кайра жүктөөнү мажбурлоо.

Чынында, эгерде ошол кире бериштеги чыңалуу дагы эле эң жогору болсо, эч нерсе өзгөрбөйт жана көзөмөл аман -эсен уланат (жогорудагы 4 -сүрөткө шилтеме берүү менен, бул 0 жана 1 циклди кайталоо). Башка жагынан алганда, эгерде ошол кирүүдөгү чыңалуу кокусунан башка киргизүүдөн төмөн болсо, анда маанини кайра жүктөө DCMP модулуна жаңы максималдуу мааниге салыштырганда OUT+ импульсун чыгарууга мүмкүнчүлүк берет (бул 2 жана 3 циклинин кайталанышынын учуру).

Көйгөйдү жеңүү үчүн бир логикалык схема керек. Ал цикл чыныгы максималдуу киришке жеткенде SPI компонентине саат сигналын жаратышы керек, ошону менен SPI Буфер Реестрине анын жаңыртылган маалымат сөзүн кайра жүктөөгө мажбур кылат. Бул төмөндөгү 7.2 жана 7.6 бөлүмдөрдө талкууланат.

5 -кадам: Түзмөктүн конфигурациясы - Matrix0 Circuit

SLG46620G 2 Матрицадан турган блокторго ээ. 2 -сүрөттө көрсөтүлгөндөй. Төмөнкү цифралар тиешелүү түзмөктүн конфигурациясын көрсөтөт.

Райондун жогорку бөлүгү - бул 3 DFF (DFF0, DFF1 жана DFF2) менен ишке ашкан "Loop Register". Киргизүү мультиплексорунун ар бир циклинен кийин 7 сегменттүү дисплей драйверине "жеңүүчү" деген экилик номерди жөнөтүү жаңыртылат, бул акыркы сканердеги эң жогорку чыңалуудагы кириш. DFFлерге сааттар да, маалыматтар да Matrix1де логикадан келип чыгат, тиешелүүлүгүнө жараша, P12, P13, P14 жана P15 порту аркылуу.

Төмөнкү бөлүгү аналогдук алдыңкы учу, Pin 8ге кириши менен x1 кирешеси менен PGA. ADC INT чыгышы SPIдин саат логикасына да, P0 порт аркылуу Matrix1ге да барат, ал ишке киргизилген эсептегич үчүн саат сигналы катары кызмат кылат.

ADC жана SPI параллелдүү маалымат чыгуулары Matrix1деги DCMP компонентине туташуу үчүн NET11 жана NET15 деп белгиленген.

6 -кадам: Түзмөктүн конфигурациясы - SPI Clocking Logic

Мурда "Логиканы ишке ашыруу" бөлүмүндө айтылгандай, SPI Буфер Реестри ар бир жолу жаңыртылып турат, чыныгы сакталган баалуулук менен ADC конверсиясынын жаңы маалыматтарынын ортосундагы салыштыруу DCMP OUT+ өндүрүшүндө импульс жаратат.

Сигналдын бүтүндүгү, эгерде бул сигнал ADC INT чыгуусу менен ЖАНА-ред болсо камсыздалат. Бул кандайдыр бир өсүштөн жана жалган козгоодон сактайт.

Биз ошондой эле туюк кырдаалды өткөрүп жиберүү үчүн, цикл чыныгы жеңүүчү маалыматына жеткенде, SPI Буфери жаңыртылышы керектигин баса белгиледик.

Туура SPI сааты үчүн оюнда үч сигнал бар:

1. ADC INT чыгаруу (LUT0-IN1)

2. DCMP OUT+ чыгаруу (порт P10 аркылуу LUT0-IN0)

3. Count Latch сигналына барабар (P11 порт аркылуу LUT0-IN2)

Биринчи экөө AND-ed жана экөө тең OR-ed менен экинчиси LUT0до, анын аткарылышы Figure 6дагыдай конфигурацияланган.

7 -кадам: Түзмөктүн конфигурациясы - Matrix0 компоненттеринин касиеттери

Figures 7-10 Matrix0 таандык калган компоненттери мүлк терезелерин көрсөтөт.

8 -кадам: Түзмөктүн конфигурациясы - Matrix1 Circuit

9 -кадам: Түзмөктүн конфигурациясы - 3 -бит бинардык эсептегич

Райондун жогорку бөлүгүндө логикалык элементтер бар, негизинен 3-бит бинардык эсептегич, буга чейин айтылгандай, ADC INT чыгаруусу менен иштейт. Бул эсептегич 12 -сүрөттө көрсөтүлгөндөй "стандарт" схемасы менен ишке ашырылат.

Бул эсептегич биздин долбоордо Flip-Flops DFF9, DFF10, DFF11 жана INV1, LUT4, LUT8 аркылуу ишке ашат. DFF9 чыгаруу LSB, ал эми DFF11 - MSB, Figure 13тө көрсөтүлгөндөй.

LUT4 XOR катары конфигурацияланган, ал эми LUT8 Figure 12деги AND-XOR логикасын аткарат.

Эсептегичтер тышкы аналогдук мультиплексорго кайрылуу үчүн үч санариптик чыгуучу казыкка барат.

LUT10 сканер бүткөндө эсептегичтин кодун чечет жана DLY8 жана P12 порт аркылуу Matrix0 импульсун берет. Бул жөн гана эсептегичтин жыйынтыгын AND-киргизүү менен ишке ашат, ошону менен 7 dec (0b111 экилик, циклдин аягы) санын декоддоо.

10 -кадам: Түзмөктүн конфигурациясы - 3 -бит логиканы салыштыруу

15 -сүрөттө учурдагы "жеңүүчү" дареги кайталанганын аныктоо үчүн колдонулган схема көрсөтүлгөн. Бул учурда, буга чейин талкуулангандай, санарип импульс мүмкүн болгон туңгуюк кырдаалды чечүү үчүн учурдагы АДКнын натыйжасын кайра жүктөөгө мажбур кылышы керек.

"Жеңүүчү" дареги Matrix1дин убактылуу реестринде сакталат (төмөндө караңыз), ал эми учурдагы дарек бинардык эсептегич тарабынан чыгарылат.

XNOR дарбазалары эки киргизүү тең болгондо чыныгы (логика 1 же "жогорку") чыгууну камсыз кылат. ЖАНА бул сигналды бардык биттер үчүн (LUT9) экилик коддору бирдей болгондо бизге импульс берет. Паритетти текшерүүчү катары XOR дарбазалары тууралуу чоо -жайын маалымдамадан тапса болот.

"Counter-equals-Latch" сигналы P11 порт аркылуу Matrix0ге берилет.

11 -кадам: Түзмөктү конфигурациялоо - Санариптик логиканы жана убактылуу каттоону

Figure 11дин төмөнкү бөлүгү (Figure 16да баса белгиленген) DCMP блогун көрсөтөт, бул долбоордун чечим кабыл алуу бөлүгү.

DFF6, 7 жана 8 цикл иштеп жатканда убактылуу "Winner" киргизүү номерин сактоо үчүн 3-биттик реестрди түзөт. Флип-флопторго киргизүү-бул 3-бит бинардык эсептегичтер, алар 11-сүрөттөгү глобалдык Matrix1 схемасында көрүнүп турат, бул жерде түшүнүктүү болуш үчүн өткөрүп жиберилген.

Бул реестрдин жыйынтыктары 7 сегменттүү дисплейди түз башкара албайт, анткени бул жерде сакталган маани сканерлөө учурунда өзгөрөт жана сканердин аягында гана "жарактуу" деп эсептелиши керек.

Ушул себептен улам, убактылуу реестрдин чыгышы Matrix0дун Loop Реестрине матрицалар аралык P13, P14 жана P15 порттору аркылуу туташат.

ADC-SPI салыштыруу жаңы максимумга алып келгенде, убактылуу реестр DCMP OUT+ чыгаруусу менен саатталганын Figure 16да байкоо маанилүү.

Ошол эле OUT+ сигналы P10 порт аркылуу Matrix0, SPI CLK Logicке өткөрүлүп берилет.

12 -кадам: Түзмөктүн конфигурациясы - Matrix1 компоненттеринин касиеттери

Figures 17-19 Matrix1ге таандык болгон компоненттердин мүлк терезелерин көрсөтөт.

13 -кадам: Жыйынтыктар

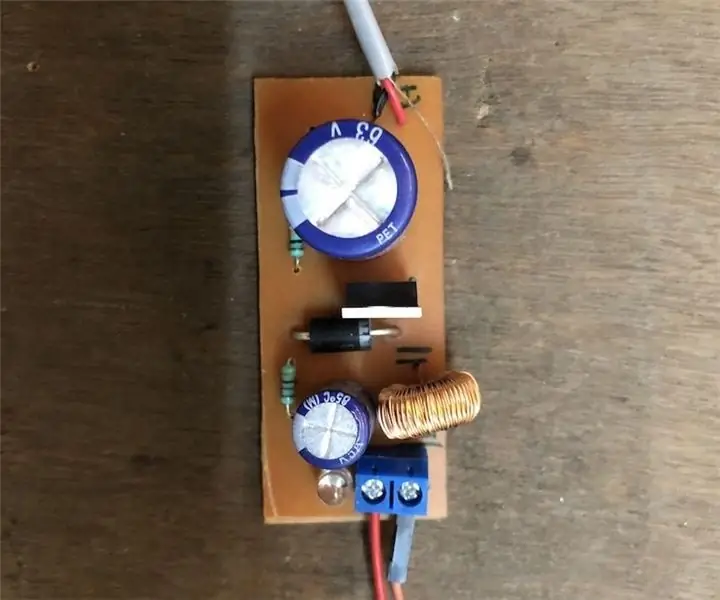

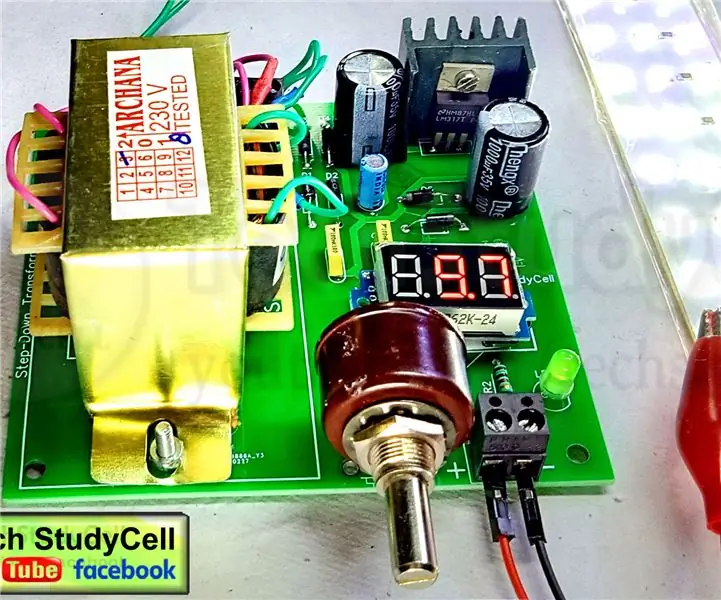

Ишке ашырууну текшерүү үчүн, баалоо тактасынын прототипи түзүлдү, мында 8 аналогдук кирүү чыңалуусу TrimPots менен бир катар резистордук бөлгүчтөр тарабынан алынат (Figure 20де көрсөтүлгөн).

Колдонулган мультиплексор - бул ADG508, бир бөлүк (12 В) менен иштей алат.

7 сегменттүү дисплей драйвери 74LS47. Бул параллель киргизүү сөзүн чечмелейт жана 7-сегменттүү жалпы аноддук дисплейди түздөн-түз айдайт.

Баалоо тактасында 2x10 тик бурчтуу туташтыргычы бар.

GreenPAK Advanced Development Platform менен биргеликте тез текшерүү үчүн сигналдарды өлчөөнү абдан жөнөкөй кылат. Мисалы, Figure 22 HP 54620A логикалык анализатору тарабынан тартылган сигналдардын топтомун (тиешелүүлүгүнө жараша CLOCK, ADC INT чыгаруу жана DCMP OUT+ чыгаруу) көрсөтөт. Толкун формалары OUT+ сигналынын көтөрүлүүчү чети менен шартталган ('A> B' деп белгиленген), аналогдук кирүүлөрдүн арасында жаңы максималдуу чыңалуу табылганда бул толкун формасын тартуу. Чынында, бул 22 -сүрөттө көрсөтүлгөн тиешелүү чыңалууну жогорулатуу үчүн Баалоо кеңешинин TrimPots бирин айлантуу аркылуу алынган.

23 -сүрөттө Баалоо кеңешинин схемасы көрсөтүлгөн.

Жыйынтык

Бул Нускамада, биз көп каналдуу башкаруу системаларына жалпы кошумча катары колдонула турган сегиз каналдуу макс (же мин) чыңалуу тапкычын ишке ашырдык. Презентация GreenPAK компоненттеринин өркүндөтүлгөн өзгөчөлүктөрүн колдонот жана аналогдук жана санариптик функцияларды бир чипке кантип кошууга болорун көрсөтөт. Бир нече коммерциялык IC'лерди Dialog GreenPAK менен алмаштырса болот, андыктан колдонмонун көлөмүн жана баасын төмөндөтсө болот.

Сунушталууда:

DIY чөнтөк өлчөмү DC Voltage Meter: 5 кадам

DIY чөнтөк өлчөмү DC чыңалуу өлчөгүчү: Бул көрсөтмөдө мен DIY чөнтөк өлчөмүн DC чыңалуу өлчөгүчүн пьезо -зумзер менен кантип өзүң текшерүү керектигин көрсөтөм. Сизге керектүү нерселердин баары электроника боюнча негизги билим жана бир аз убакыт.Эгер сизде кандайдыр бир суроо же көйгөй болсо, анда сиз

Max MSP Ambient Loop Generator: 19 кадам

Max MSP Ambient Loop Generator: Бул Max MSPде чөйрө циклинин генераторун түзүүнү кантип баштоо керектиги боюнча окуу куралы. Бул окуу куралы сизде Max MSP, DAW интерфейстери жана сигналдарды иштетүү боюнча негизги түшүнүк бар деп күтөт. Эгерде сиз бул үйрөткүчтө иштелип чыккан программаны колдонууну кааласаңыз

DC - DC Voltage Step Down Switch Mode Бак Voltage Converter (LM2576/LM2596): 4 кадам

DC-DC Voltage Step Down которуу режими Бак Voltage Converter (LM2576/LM2596): Жогорку натыйжалуу Бак Конвертерин жасоо-бул оор жумуш, ал тургай тажрыйбалуу инженерлер бир нече конструкцияны талап кылат. бул DC-to-DC кубат өткөргүчү, ал чыңалууну төмөндөтөт (жогорулатууда

LM317 Voltage Regulator колдонуу менен жөнгө салынуучу Voltage DC Power Supply: 10 кадам

LM317 Voltage Regulator колдонуу менен жөнгө салынуучу Voltage DC Power Supply: Бул долбоордо, мен LM317 электр менен камсыз кылуу схемасы менен LM317 ICди колдонуп, жөнгө салынуучу чыңалуу DC DC менен камсыз кылдым. Бул схемада курулган көпүрө түзөткүчү бар болгондуктан, биз 220V/110V AC киргизүүнү түз туташтыра алабыз

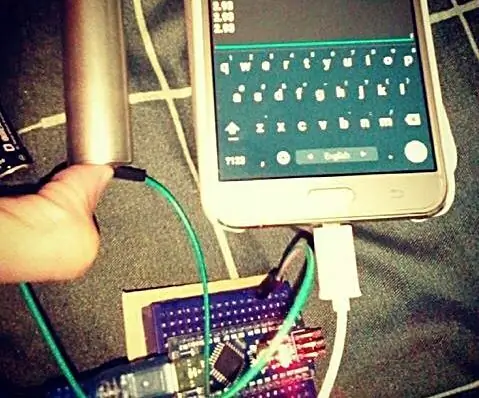

ОКУУ ANALOG VOLTAGE - ARDUINO - CODE REVEAL #1: 5 Steps

ОКУУ ANALOG VOLTAGE - ARDUINO - CODE REVEAL #1: CODE REVEAL #1 REAL REAL ANALOG VOLTAGE: Бул мисал аналогдук пинге 0 аналогдук кирүүнү кантип окууну, analogRead () ден чыңалууга айландырууну жана аны серияга басып чыгарууну көрсөтөт Arduino программалык камсыздоонун монитору (IDE)