Мазмуну:

- 1 -кадам: Vivado HLS деген эмне?

- 2 -кадам: HLS Video Library

- 3 -кадам: синтездөө

- 4 -кадам: Версиялоо жана экспорттоо үчүн башка маалыматтар

- 5 -кадам: Vivado IP китепканасына экспорттоо

- 6 -кадам: Синтез жана экспорттук анализ

- 7 -кадам: Vivadoдогу IP китепканасын кошуу

- 8 -кадам: Жаңыртууну жасоо

- 9 -кадам: Кошумча маалымат жана маалымат

- 10 -кадам: Чыгуу жана киргизүү

- 11 -кадам: AXI Register Interfacing

- 12 -кадам: Dataflow Pragma

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 10:42.

- Акыркы өзгөртүү 2025-01-23 14:53.

Сиз качандыр бир убакытты же камтылган системаны кошпостон видеону реалдуу убакытта иштетүүнү кааладыңыз беле? Бул үчүн кээде FPGAs (Field Programmable Gate Arrays) колдонулат; бирок, VHDL же Verilog сыяктуу аппараттык спецификация тилдеринде видео иштетүү алгоритмдерин жазуу эң эле көңүлдү чөгөрөт. C ++ чөйрөсүндө программалоого жана андан аппараттык спецификация тилинин кодун түзүүгө мүмкүндүк берген Vivado HLS, Xilinx куралын киргизиңиз.

Керектүү программалар:

- Vivado HLS

- Vivado

- (Эгерде сиз AXI регистрлерин колдонсоңуз) Vivado SDK

(Милдеттүү эмес) Xilinxтин мисалдарын бул жерден жүктөп алыңыз:

Xilinx HLS видео мисалдары

1 -кадам: Vivado HLS деген эмне?

Vivado HLS - бул c ++ сыяктуу кодду FPGAда ишке ашырыла турган аппараттык структураларга айландыруу үчүн колдонулган курал. Vivado менен колдонуу үчүн.

Тиркелген файлдарды жүктөп алып, долбооруңузду түзө турган жерге коюңуз. (эгерде алар рандомизацияланган атка ээ болсо, аларды "top.cpp" жана "top.h" деп кайра атагыла)

2 -кадам: HLS Video Library

HLS Video Library бул макалада шилтеме дизайны бар документтерге ээ: XAPP1167 Дагы бир жакшы булак бул жөнүндө Xilinx Wiki баракчасы.

Vivado HLSти баштаңыз.

Жаңы долбоор түзүү.

Мурунку кадамда жүктөлгөн файлдарды алыңыз жана аларды баштапкы файлдар катары кошуңуз. (Эскертүү: файлдар долбоорго көчүрүлбөйт, тескерисинче алар турган жерде калат)

Андан кийин Browse баскычын колдонуп, жогорку функцияны тандаңыз.

Кийинки бетте сиз колдонуп жаткан Xilinx бөлүгүн тандаңыз.

3 -кадам: синтездөө

Solution => Run C Synthesis => Active Solution

~ 227.218 секунддан кийин, муну жасоо керек. (Эскертүү: сиздин чыныгы синтез убактыңыз көптөгөн факторлорго жараша өзгөрүп турат)

4 -кадам: Версиялоо жана экспорттоо үчүн башка маалыматтар

Версия номерлери Vivado менен өз ара аракеттенишип, сиз дизайндагы IPди жаңырта аласыз. Эгерде бул кичинекей версияны өзгөртүү болсо, анда аны өз ордунда кылса болот, ал эми негизги версияны өзгөртүү кол менен жаңы блокту кошуп, эскисин алып салууну талап кылат. IP баскычын басуу менен толугу менен автоматтык түрдө жасалат. Сиз IP статусун көрүү үчүн Vivado tcl консолунда "report_ip_status" иштете аласыз.

Чыгаруу => Чыгаруу Орнотууларында версиянын номерлерин жана башка маалыматты коюңуз …

Же болбосо, бул орнотууларды экспорттоо учурунда коюуга болот.

5 -кадам: Vivado IP китепканасына экспорттоо

Чечим => RTL экспорттоо

Эгер мурунку кадамда IP китепканасынын чоо -жайын орнотпогон болсоңуз, азыр муну кыла аласыз.

6 -кадам: Синтез жана экспорттук анализ

Бул экранда биз экспорттолгон модулубуздун статистикасын көрө алабыз, бул биздин 10нс (100МГц) мезгилибизге жооп берерин жана ал ар бир ресурстун канча бөлүгүн колдоноорун көрсөтөт.

Мунун айкалышы менен, Synthesis Report жана Dataflow анализи, биз 317338 сааттык циклди талап кыларын көрө алабыз * 10нс мезгил мезгили * 14 түтүк этаптары = 0.04442732 секунд. Сүрөттү иштетүү менен коштолгон жалпы күтүү секунданын жыйырмадан биринен аз экенин билдирет (максаттуу 100МГц жыштыгында).

7 -кадам: Vivadoдогу IP китепканасын кошуу

Синтезделген IP блогуңузду колдонуу үчүн аны Vivadoго кошууңуз керек.

Vivado'до IP каталогуна өтүп, "Репозиторийди кошуу …" баскычын оң баскыч менен чыкылдатып, долбооруңузга IP кампасын кошуңуз.

Vivado HLS долбооруңуздун каталогуна өтүңүз жана чечим каталогун тандаңыз.

Ал тапкан IP жөнүндө билдириши керек.

8 -кадам: Жаңыртууну жасоо

Кээде сиз HLS блогун Vivado дизайнына киргизгенден кийин өзгөртүүлөрдү киргизишиңиз керек.

Бул үчүн, сиз өзгөртүүлөрдү киргизип, кайра синтездей аласыз жана IPди жогорку версия номери менен экспорттой аласыз (чоң/кичине версия номеринин өзгөрүшү жөнүндө мурунку кадамдагы чоо -жайын караңыз).

Жаңы версияны экспорттоону өзгөрткөндөн кийин, Vivadoдогу IP репозиторийлериңизди жаңыртыңыз. Муну Vivado репозиторийде IP өзгөргөнүн байкаганда же кол менен иштетилгенде жасаса болот. (Эскертүү, эгер сиз IP репозиторийлериңизди баштагандан кийин жаңыртсаңыз, бирок экспорттоо HLSте аяктаганга чейин, IP убактылуу жок болот, анын бүтүшүн күтүп, кайра жаңыртыңыз.)

Бул жерде дискте IP өзгөргөндүгү жөнүндө маалымат бар терезе пайда болушу керек жана аны "Тандалганды жаңыртуу" баскычы менен жаңыртууга мүмкүнчүлүк берет. анда бул баскычты басуу эски IPди автоматтык түрдө жаңысына алмаштырат, антпесе көбүрөөк иш талап кылынышы мүмкүн.

9 -кадам: Кошумча маалымат жана маалымат

Төмөнкү кадамдар HLS синтези кандай иштээри жана аны менен эмне кыла алаарыңыз жөнүндө көбүрөөк маалымат берет.

HLS синтезделген IP блогун колдонгон долбоордун мисалы үчүн, бул нускаманы караңыз.

10 -кадам: Чыгуу жана киргизүү

Акыркы IP блогуна чыгуулар жана кириштер синтезатордун жогорку функциянын ичиндеги жана сыртындагы маалымат агымынын анализинен аныкталат.

VHDL же verilog сыяктуу эле, HLS сизге IP ортосундагы байланыштар жөнүндө деталдарды көрсөтүүгө мүмкүндүк берет. Бул саптар буга мисал:

жараксыз image_filter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE огу порт = video_in bundle = INPUT_STREAM #pragma HLS INTERFACE огу порт = video_out bundle = OUTPUT_STREAM #pragma HLS INTERFACE s_axilite port = x bundle = CONTROL_BUS offset = Hx_setset = 0x14 #prxma

Сиз IP блогунда көрсөтүлгөн портторго бул көрсөтмөлөрдүн кандай таасир эткенин көрө аласыз.

11 -кадам: AXI Register Interfacing

IP блогуңуздан PSге кирүүнү/чыгууну алуу үчүн муну жакшы жол AXI интерфейси аркылуу.

Сиз муну HLS кодуңузда көрсөтө аласыз, анын ичинде кийинчерээк баалуулукка жетүү үчүн колдонула турган офсеттер:

жараксыз image_filter (AXI_STREAM & video_in, AXI_STREAM & video_out, int & x, int & y) {

#pragma HLS INTERFACE s_axilite порт = x таңгак = CONTROL_BUS офсет = 0x14

#pragma HLS INTERFACE s_axilite port = y bundle = CONTROL_BUS offset = 0x1C #pragma HLS dataflow

x = 42;

y = 0xDEADBEEF; }

Vivado'до туура туташкандан кийин, Vivado SDK бул кодду колдонуу менен баалуулуктарга кире аласыз:

#"paramet.h" кошуу

#define xregoff 0x14 #define yregoff 0x1c x = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+xregoff); y = Xil_In32 (XPAR_IMAGE_FILTER_0_S_AXI_CONTROL_BUS_BASEADDR+yregoff);

Муну менен сиз 42 -жылы x менен 0xdeadbeef аласыз

12 -кадам: Dataflow Pragma

#Pragma DATAFLOW ичинде коддун ишке ашыруу жолу кадимки С ++ тилинен өзгөрөт. Код бардык маалыматтын ар кайсы бөлүгүндө дайыма иштей тургандай кылып өткөрүлүп берилген (Муну заводдо конвейердик линия сыяктуу ойлонуп көрүңүз, ар бир станция тынымсыз бир функцияны аткарып, кийинки станцияга өткөрүп берет)

сүрөттөн сиз директивалардын ар бири экенин көрө аласыз

Кадимки өзгөрмөлөр болуп көрүнгөнүнө карабастан, img объекттери чындыгында командалардын ортосунда кичине буфер катары ишке ашырылат. Сүрөттү функцияга киргизүү катары колдонуу аны "керектейт" жана аны колдонууга жараксыз кылат. (Демек, кайталанган буйруктарга муктаждык бар)

Сунушталууда:

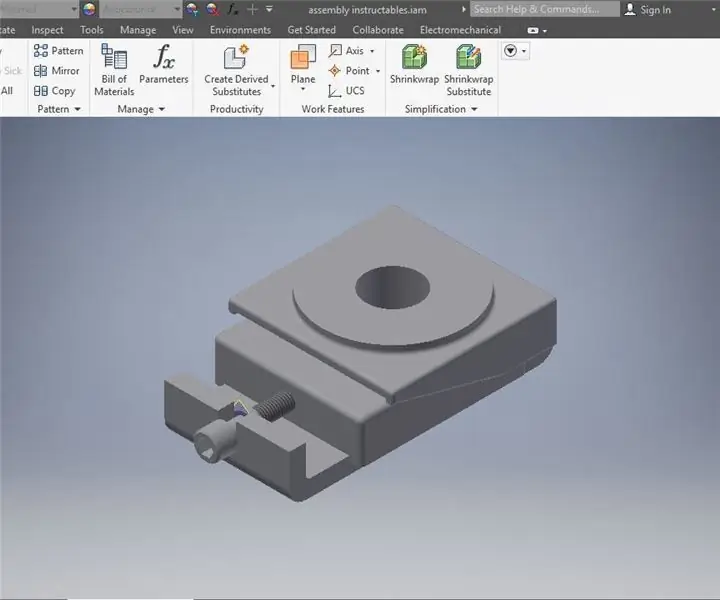

Тегиздөө блогунун монтаждоо ийгилиги: 30 кадам

Тегиздөө блогунун ийгилиги: Бул доктор Дуглас Лекорчиктин Берада колледжинин TAD 330 классындагы акыркы техникалык жазуусу, Кармадри Сантьяго 28 -жылдын 2020 -апрелинде

Үн ийилүү синтези: 14 кадам (сүрөттөр менен)

Үн ийилүү синтези: Мен буга чейин бир нече үн ийилүүчү машиналарды кургам (төмөндөгү "ibles" шилтемелерин караңыз). Бул жолу мен реверб жана амп модулун коштум, ал чындап эле сизге жаңы үндөрдүн диапазонун берет. Мындан тышкары, үн жазгыч модулу колдонулган

Ретро сүйлөө синтези. Бөлүм: 12 IoT, Үйдү автоматташтыруу: 12 кадам (Сүрөттөр менен)

Ретро сүйлөө синтези. Бөлүм: 12 IoT, Үйдү автоматташтыруу: Бул макала IoT Retro Speech Synthesis түзмөгүн учурдагы үй автоматташтыруу тутумуна кантип түзүү жана интеграциялоону документтештирүүчү үй автоматташтыруу боюнча сериядагы 12 -макаланы камтыйт

Vivado Simluation кантип колдонсо болот: 6 кадам

Vivado Simluation кантип колдонсо болот: Мен бул симуляция долбоорун онлайн сабагы үчүн жасадым. Долбоор Verilog тарабынан жазылган. Биз Vivado'до симуляцияны колдонуп, толкун формасын enable_srде (цифраны иштетүү) мурда түзүлгөн токтоочу саат долбоорунан элестетебиз. Мындан тышкары, биз

Компьютериңиздеги аналогдук үн синтези: 10 кадам (сүрөттөр менен)

Компьютериңиздеги аналогдук үн синтези: Ошол эски аналогдук синтезаторлордун үнүнө окшошпу? Өз убактыңызда, өз жериңизде, каалаганча АКЫСЫЗ ойноону каалайсызбы? Бул жерде сиздин эң жапайы Moog кыялдарыңыз орундалат. Сиз электрондук жазуучу же сүрөтчү боло аласыз