Мазмуну:

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 10:41.

- Акыркы өзгөртүү 2025-01-23 14:51.

Бул долбоордун максаты - Smart Mirrorдун сүрөтүн көрсөтүү функциясын түзүү. Күзгү прогноздорду (күнөстүү, жарым -жартылай күнөстүү, булуттуу, шамалдуу, жамгыр, күн күркүрөө, кар) жана -9999 ° дан 9999 ° чейин температуранын маанисин көрсөтө алат. Божомолдоо жана температуранын мааниси аларды аба -ырайынын APIсинен талдоого окшоштуруу үчүн катуу коддолгон.

Долбоор FreeRTOS менен иштеген Zynq-Zybo-7000 тактасын колдонот жана аппаратты долбоорлоо жана программалоо үчүн Vivado 2018.2ди колдонот.

Бөлүктөр:

Zynq-Zybo-7000 (FreeRTOS менен)

19 ЖК (640x480)

VGA кабели

12 "x 18" акрил күзгү

1 -кадам: Vivado конфигурациясы

Vivado 2018.2ди Xilinxтен жүктөп алып, Webpack лицензиясын колдонуңуз. Vivado менен "Жаңы проект түзүү" программасын ишке киргизип, ага ат коюңуз. Андан кийин "RTL долбоорун" тандап, "Учурда булактарды көрсөтпөөнү" текшериңиз. Бөлүктү тандоодо "xc7z010clg400-1" тандап, кийинки беттеги "Аяктоо" баскычын басыңыз.

2 -кадам: VGA Driver IP пакеттөө

Vga_driver.sv файлын Дизайн булактарына кошуңуз. Андан кийин, "Куралдарды" чыкылдатып, "Жаңы IP түзүү жана топтоо" дегенди тандаңыз. "Учурдагы долбооруңузду пакеттөө" дегенди тандаңыз. Андан кийин IP ордун тандап, ".xci файлдарын кошуу." Калкып чыкмадан "ОК" чыкылдатып, анан "Аяктоо".

"Packaging Steps" жөнүндө "Review and Package" бөлүмүнө өтүп, "Package IP."

Эми vga_driver IP -блок катары жеткиликтүү болушу керек.

3 -кадам: Zynq IP

"IP интегратору" бөлүмүнүн астынан "Блок дизайнын түзүүнү" тандаңыз. "ZYNQ7 иштетүү системасын" кошуп, блокту эки жолу чыкылдатыңыз. "Импорттоо XPS Орнотууларын" чыкылдатып, ZYBO_zynq_def.xml файлын жүктөңүз.

Андан кийин, "PS-PL конфигурациясы" астында "AXI Non Secure Enablement" ачылуучу тизмесин ачыңыз жана "M AXI GP0 интерфейсин" текшериңиз.

Андан кийин, "MIO конфигурациясы" астында "Колдонмо процессорунун бирдиги" ачылуучу тизмесин ачып, "Таймер 0" менен "Күзөтчүнү" текшериңиз.

Акырында, "Саатты Конфигурациялоо" бөлүмүнүн астында "PL Fabric Clocks" ачылуучу тизмесин ачып, "FCLK_CLK0" жана 100 МГцте текшериңиз.

4 -кадам: GPIO IP

Блок Дизайнына эки GPIO блогун кошуңуз. GPIO пикселдердин дарегин жана RGB компоненттерин көзөмөлдөө үчүн колдонулат. Жогорудагы сүрөттөрдө көрсөтүлгөндөй блокторду конфигурациялаңыз. Эки блокту кошуп жана конфигурациялагандан кийин, "Connection Automationти иштетүү" дегенди басыңыз.

GPIO 0 - 1 -канал пиксел дарегин, 2 -канал кызыл түстү көзөмөлдөйт.

GPIO 1 - 1 -канал жашыл түстү, 2 -канал көк түстү башкарат.

5 -кадам: Эстутумду бөгөттөө

Блоктун эс тутум генераторунун IP блогун Блок Дизайнына кошуңуз жана жогоруда көрсөтүлгөндөй конфигурациялаңыз. Пикселдик түстөр эс тутум даректерине жазылат, аларды VGA драйвери окуйт. Дарек сабы колдонулуп жаткан пикселдердин санына дал келиши керек, андыктан ал 16 бит болушу керек. Маалыматтар дагы 16 бит, анткени 16 түстүү бит бар. Биз кандайдыр бир моюнга алуу биттерин окууга көңүл бурбайбыз.

6 -кадам: Башка IP

Тиркелген pdf бүткөн Блок Дизайнын көрсөтөт. Жетишпеген IPди кошуп, туташууларды аягына чыгарыңыз. Ошондой эле VGA түстүү чыгымдары жана вертикалдуу жана горизонталдуу синхрондоштуруу үчүн "Сырткы нерселерди жасаңыз".

xlconcat_0 - Жеке түстөрдү бириктирип, Block RAMге киргизилген бир 16 биттик RGB сигналын түзөт.

xlconcat_1 - VGA драйверинин мамыча жана катар сигналдарын бириктирет жана Block RAMдин В портуна берилет. Бул VGA драйверине пиксел түсүнүн маанилерин окууга мүмкүнчүлүк берет.

VDD - Үзгүлтүксүз Жогорку блоктун RAM жазуу мүмкүнчүлүгүнө туташкан, ошондуктан биз ага дайыма туура боло алабыз.

xlslice_0, 1, 2 - Кесимдер RGB сигналын VGA драйверине берилүүчү жеке R, G жана B сигналдарына бөлүү үчүн колдонулат.

Блок Дизайн аяктагандан кийин, HDL орогучун түзүңүз жана чектөөлөр файлын кошуңуз.

*Блок дизайны benlin1994 тарабынан жазылган окуу куралына негизделген*

7 -кадам: SDK

Бул Блок Дизайнын иштеткен код төмөндө камтылган. Init.c чиймени башкаруучу функцияларды камтыйт (прогноздор, сандар, даража белгиси ж. Б.). Main.c'теги негизги цикл - бул такта программалангандан кийин иштей турган нерсе. Бул цикл болжолдоонун жана температуранын маанилерин белгилейт, андан кийин init.c.де тартуу функцияларын чакырат. Учурда ал жети прогнозду карап чыгат жана биринин артынан экинчисин көрсөтөт. Ар бир сүрөттү көрүү үчүн 239 -сапка үзүлүү чекитин кошууңуз сунушталат. Код комментарийленген жана сизге көбүрөөк маалымат берет.

8 -кадам: Жыйынтык

Учурдагы долбоорду жакшыртуу үчүн, COE файлдары түрүндө алдын ала жүктөлгөн болжолдуу сүрөттөрдү Block Memory Generatorго жүктөө мүмкүн. Ошентип, болжолдорду C кодундагыдай кол менен түзүүнүн ордуна, сүрөттөрдү окууга болот. Биз муну жасоого аракет кылдык, бирок иштей алган жокпуз. Биз пикселдик баалуулуктарды окуп, аларды чыгара алдык, бирок ал RAMге жүктөгөндөргө окшобогон башаламан сүрөттөрдү жаратты. Block Memory Generator маалымат барагын окуу пайдалуу.

Долбоор негизинен Smart Mirrorдун жарымы, анткени ал интернетке туташуу жагын жоготкон. Муну кошуу толук Smart Mirror берет.

Сунушталууда:

Чексиздик күзгү саатын жасаңыз: 15 кадам (сүрөттөр менен)

Чексиздик күзгү саатын жасаңыз: Мурунку долбоордо мен чексиздик күзгүсүн кургам, ал жерде менин акыркы максатым аны саатка айландыруу болгон. (Түстүү чексиздик күзгүсүн жасаңыз) Мен аны кургандан кийин умтулган жокмун, анткени ал сонун көрүнгөнү менен, кээ бир нерселер бар болчу

Кара күзгү: 4 кадам

Кара күзгү: Бул долбоор менин акылдуу күзгү жасоого болгон аракетим болчу. Бул долбоордун максаты менин күзгүдөн дагы эле көрүнүп турган сааты бар күзгү түзүү болчу. Ошентип, эртең менен даярданып жатканыңызда, убакыт жетти. Мен да жарнамалоого аракет кылдым

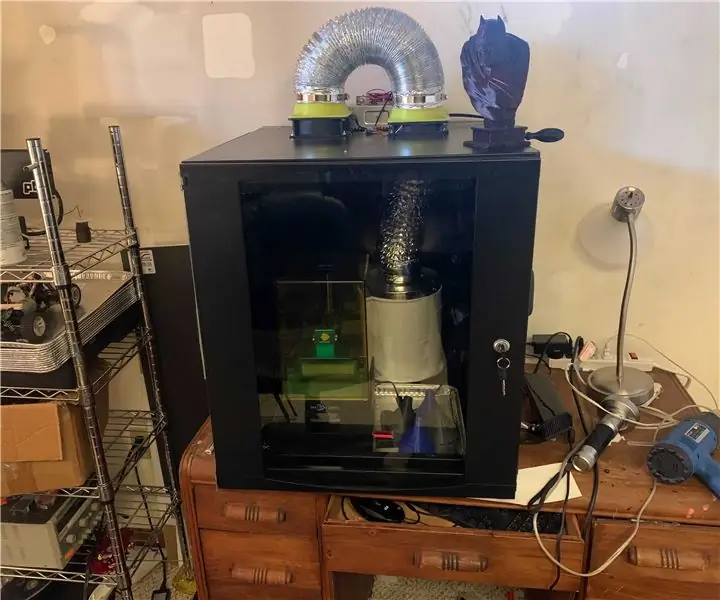

Кантип портативдүү акылдуу күзгү түзүү/куту айкалышын түзүү: 8 кадам

Кантип портативдүү акылдуу күзгү түзүү/куту айкалыштыруу: Дэвистеги капстоюнум үчүн акыркы долбоор катары & Элкинс колледжи, мен порт катары иштей турган чоң күзгү жана малина пи жана сыйкырдуу күзгү программалык платформасын колдонуу менен бирге саякат кутусун иштеп чыгууну чечтим

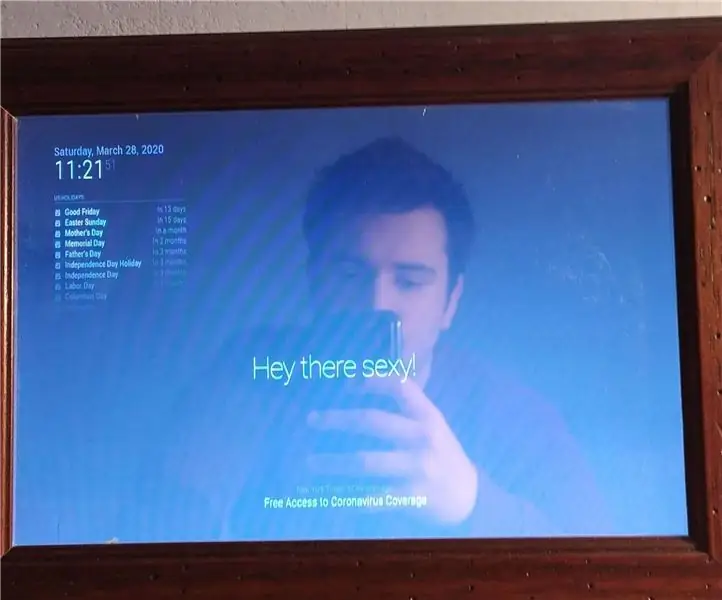

Raspberry Pi 4 менен акылдуу күзгү кантип курулат: 10 кадам

Raspberry Pi 4 менен акылдуу күзгү кантип курулат: Бул колдонмодо биз сүрөт алкагы, эски монитор жана сүрөт айнеги сыяктуу кайра иштетилген бөлүктөрдү колдонуп, акылдуу күзгү кантип курууну көрөбүз. .com

DIY акылдуу күзгү кантип жасалат: 12 кадам (сүрөттөр менен)

DIY акылдуу күзгү кантип жасалат: A " Акылдуу күзгү " эки тараптуу күзгү, анын артында дисплей бар, ал, адатта, убакыт жана күн, аба ырайы, календарь жана башка бардык нерселер сыяктуу пайдалуу маалыматты көрсөтүү үчүн колдонулат! Адамдар аларды ар кандай максатта колдонушат