Мазмуну:

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 10:40.

- Акыркы өзгөртүү 2025-01-23 14:51.

Бул көрсөтмөдө биз RTLде жөнөкөй VGA контроллерин иштеп чыгалы деп жатабыз. VGA Controller - бул VGA дисплейлерин айдоого арналган санариптик схема. Бул көрсөтүлө турган кадрды чагылдырган Frame Bufferден (VGA Memory) окуйт жана көрсөтүү үчүн керектүү маалыматтарды жана синхрондоштуруу сигналдарын жаратат.

Эгерде сиз Verilog/System верилогунун кодун издесеңиз: Verilogдагы VGA Controller жана Video System блогума баш багыңыз

1 -кадам: VGA контроллеринин интерфейси

Төмөндө VGA контроллериндеги негизги интерфейс сигналдары келтирилген

- Пикселдик саат же VGA сааты

- HSYNC жана VSYNC сигналдары

Тандалган VGA дисплейи үчүн, адегенде аны айдоого керектүү Pixel Clock жыштыгын эсептөө керек. Бул 3 параметрден көз каранды: Жалпы горизонталдык пикселдер, жалпы вертикалдуу пикселдер, экранды жаңыртуу ылдамдыгы.

Адатта, F = THP * TVP * Refresh Rate

Ар кандай VGA дисплейлери үчүн керектүү пикселдик сааттын документтерин тиркелген RARден табыңыз.

HSYNC жана VSYNC сигналдары Pixel саатынан түзүлөт. HSYNC жана VSYNC сигналдарынын убактысы параметрлердин санына жараша болот: горизонталдык жана вертикалдуу алдыңкы, горизонталдык жана вертикалдуу арткы, горизонталдык жана вертикалдуу дисплей пикселдери, горизонталдык жана вертикалдуу синхронизациялоочу импульстун туурасы жана полярдыктары.

Бул параметрлер тандалган VGA дисплейи үчүн стандартташтырылган. Бул документтерди тиркелген RARден табыңыз.

Бул параметрлер биздин VGA Controller IPдеги конфигурацияланган параметрлер.

2 -кадам: VGA дисплейи менен VGA контроллерин интеграциялоо

Сүрөттө VGA дисплейи менен VGA контроллерин кантип бириктирүү көрсөтүлгөн. Системаны аягына чыгаруу үчүн дагы эки компонент керек:

- Frame Buffer: Көрсөтүлө турган кадрды камтыган эстутум.

- Видео DAC: RGB санариптик маалыматын өзгөрткөн жана VGA дисплейин RGB аналогдук сигналдар менен тиешелүү чыңалуу деңгээлинде айдаган DAC.

Эң жөнөкөй жана популярдуу Video DACтердин бири ADV7125. Бул RGB санарип сөздөрдү 0-0.7 V аналогдук сигналдарга айландырган жана VGA дисплейин башкарган 8-бит DAC.

3 -кадам: Frame Buffer Дизайн

Бул көрсөтүлө турган сүрөттү "сактаган" эс. Бул адатта RAM же кээде ROM. Биз сүрөттү чагылдыруу үчүн кадрдык буферди кантип иштеп чыгууну талкуулайбыз. Frame buffer бул санариптик маалыматты VGA Controller командасы боюнча Video DACка өткөрүп берет.

Биринчиден, биз керектүү пиксел тереңдигин чечишибиз керек. Бул сүрөттүн сапатын, пикселдин түстөрүнүн түрдүүлүгүн чечет. 8-бит DAC үчүн биз пикселдин негизги түс компоненттерин көрсөтүшүбүз керек: R, G жана B ар бири 8 бит. Бул пикселдин 24 биттик экенин билдирет.

Ар бир пиксель Frame Buffer эстутумунда үзгүлтүксүз түрдө сакталат.

Көрсөтүлө турган сүрөт 800x600 пиксел дейли.

Демек, Frame Buffer 800x600 = 480000 x 24 bit эстутумуна муктаж

Эстутумдун жалпы көлөмү 800x600x24 = 1400 кБ болжол менен.

Ак -кара сүрөт болсо, 800x600x1 = 60 кБ болжол менен.

Блок RAM'лери Xilinx FPGA'ларда Frame Bufferди көрсөтүү үчүн колдонулушу мүмкүн.

4 -кадам: Эскертүүлөр

- Кошумча сигналдар тандалган DACке жараша VGA контроллеринде керек. Мен ADV7125 колдондум.

- VGA дисплейин айдоонун алдында VSYNC жана HSYNC боюнча флип-флоптор аркылуу циклдин кечигүүсүн кошуңуз. Бул DAC жана Memory кечигүүлөрүнөн улам. Пикселдик сигналдар HSYNC жана VSYNC менен синхрондоштурулушу керек. Менин учурда, бул 2 цикл кечигүү болчу.

- Эгерде берилген өлчөмдөгү Frame Buffer блоктун кочкорунун өлчөмүнө байланыштуу FPGAда иштелип чыкпаса, сүрөттү көрсөтүү үчүн кичирээк эстутумду колдонуңуз жана кодду толук кадрдын чегине эмес, жеткиликтүү эс тутумунун чегине жылдыруу үчүн кодду түзөтүңүз. Бул бүт экран боюнча бир эле сүрөттү кайталай берет. Дагы бир ыкма - бул пикселди масштабдоо, анда ар бир пиксел бүткүл сүрөттү толук экранда, азыраак токтомдо көрсөтүү үчүн кайталанат. Муну коддогу даректерди көбөйтүү логикасын өзгөртүү аркылуу жасаса болот.

- IP бардык FPGAларда толугу менен портативдүү жана Virtex-4 FPGAда 100 МГцке чейин текшерилген.

5 -кадам: Тиркелген файлдар

RAR камтыйт:

- VGA Controller коду

- VGA стандарттарынын PDF форматтары.

Сунушталууда:

VHDLде Жөнөкөй Төрт Жактуу Ассоциативдүү Кэш Контроллеринин Дизайны: 4 Кадам

VHDLдеги Төрт Жактуу Ассоциативдүү Кэш Контроллеринин Дизайны: Менин мурунку көрсөтмөмдө, биз жөнөкөй түз картага түшүрүлгөн кэш контроллерин кантип жасоону көрдүк. Бул жолу биз бир кадам алдыга жылабыз. Биз жөнөкөй төрт тараптуу ассоциативдүү кэш контроллерин иштеп чыгабыз. Артыкчылыгы? Сагынуу көрсөткүчү азыраак, бирок perfo баасында

VHDLде программалануучу үзгүлтүк контроллеринин дизайны: 4 кадам

VHDLде программалануучу үзгүлтүккө учуроочу контролердун дизайны: Мен бул блогдон алган жоопторума толуп кеттим. Рахмат балдар менин блогума кирип, сиздер менен өз билимимди бөлүшүүгө түрткү бергениңиздер үчүн. Бул жолу мен бардык SOCларда көргөн дагы бир кызыктуу модулдун дизайнын сунуштайм - Interrupt C

VHDLдеги жөнөкөй кэш контроллеринин дизайны: 4 кадам

VHDLдеги жөнөкөй кэш контроллеринин дизайны: Мен муну үйрөтүп жатам, анткени кээ бир VHDL коддорун үйрөнүү жана кэш контроллерин иштеп чыгууну баштоо кыйынга турду. Ошентип, мен нөлдөн баштап кэш контроллерин иштеп чыктым жана аны FPGAда ийгиликтүү сынап көрдүм. Менде п

PCB дизайны жөнөкөй жана оңой кадамдар менен: 30 кадам (сүрөттөр менен)

ПКБнын дизайны жөнөкөй жана оңой кадамдар менен: САЛАМ ДОСТОР ПКБ дизайнын үйрөнүүнү каалагандар үчүн анын абдан пайдалуу жана оңой үйрөткүчү башталат

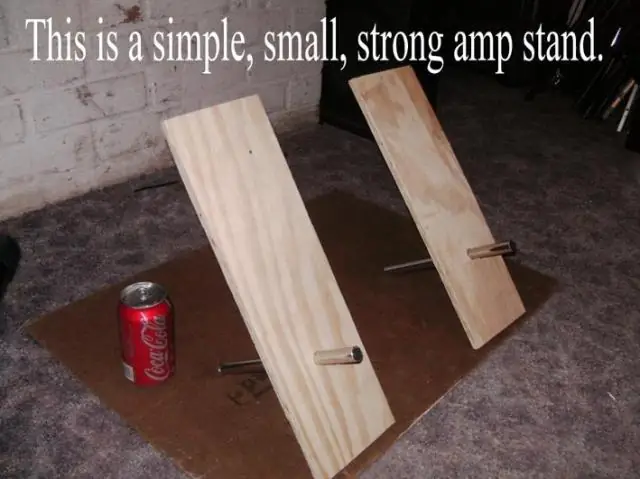

Гитара Amp Tilt стенди - "Африкалык кресло" дизайны - Жөнөкөй, Кичинекей, Күчтүү, Оңой, Акысыз же Чыныгы Арзан: 9 кадам

Гитара Amp Tilt Stand - "Африкалык кресло" Дизайн - Жөнөкөй, Кичинекей, Күчтүү, Оңой, Акысыз же Реалдуу Арзан: Гитаранын Amp Tilt Stand - Өтө Оңой - жөнөкөй, кичине, күчтүү, бекер же чыныгы арзан. Бардык өлчөмдөгү амперлер үчүн, ал тургай өзүнчө башы бар чоң шкафтар. Жөн эле тактайларды жана түтүктөрдү өзүңүз каалагандай кылып жасаңыз