Мазмуну:

- Автор John Day day@howwhatproduce.com.

- Public 2024-01-30 10:38.

- Акыркы өзгөртүү 2025-01-23 14:51.

By AmCoderhttps://www.linkedin.com/in/mituFollow Автордун дагы:

Жөнүндө: Миту Радж - Жөн эле хоббист жана үйрөнүүчү - Чип дизайнери - Программалык камсыздоону иштеп чыгуучу - Физика жана математиканын энтузиастары AmCoder жөнүндө »

## Бул синус жана косинус толкундарын жаратуу үчүн CORDIC ALGORITHMди VHDL ишке ашыруу үчүн Google'дагы эң көп чыкылдатуу, популярдуу шилтеме ## Учурда көптөгөн аппараттык эффективдүү алгоритмдер бар, бирок алар программалык тутумдардын үстөмдүгүнөн улам жакшы белгилүү эмес. көп жылдар. CORDIC - бул кандайдыр бир тригонометриялык, гиперболалык, сызыктуу жана логарифмдик функцияларды кошо алганда, көптөгөн функцияларды эсептөө үчүн колдонулган жылышуунун жана логиканын жыйындысынан башка эч нерсе болбогон алгоритм. Бул эсептегичтерде колдонулган алгоритм. Ошентип, жөн эле алмаштыргычтарды жана суммаларды колдонуу менен биз корпалдык алгоритмди колдонуп, DSP күчү анча татаал эмес аппаратты иштеп чыга алабыз. Демек, ал VHDL же Verilogдо жылаңач RTL дизайны катары иштелип чыгышы мүмкүн, ал эч кандай атайын калкып турган чекит бирдиктерин же татаал математикалык IPлерди колдонбостон.

1 -кадам: VHDL жана Modelsim

Бул жерде кордук алгоритм синус толкуну менен коса толкунун жаратуу үчүн VHDLдин жардамы менен ишке ашырылат. Бул синус жана косинус кириш бурчун абдан тактыкта чыгара алат. Код FPGAда синтезделет. Modelsim дизайнды жана сыноо стендин тууроо үчүн колдонулат.

2 -кадам: Дизайн жана сыноо стенди үчүн VHDL коду

Экилик масштабдоо ыкмасы калкып турган чекиттүү сандарды көрсөтүү үчүн колдонулат.

Сураныч, коддон мурун тиркелген документтер аркылуу өтүңүз.

Go thruSimulating cordic_v4.vhd - Дизайн - Киргизүү 32 битке бурч + белги бит; ал 0.000000000233 даражадагы тактык менен 0дөн +/- 360 градуска чейинки каалаган бурчту иштете алат. Киргизүүдө -> MSB -бул белги, ал эми калган 32 бит чоңдукту билдирет. тактык менен 0.00001526. Сураныч, тийиштүү синус же кос мааниси терс болсо, чыгуу 2дин комплимент түрүндө көрсөтүлөрүн эске алыңыз. Simulation testb.vhd - Дизайн үчүн сыноо стенди (1) Киргизүү бурчтары жана баштапкы абалга келтирүү = '0'. Симуляциянын эки кадамынан кийин "1" жана "бардыгын иштетүү" абалына келтириңиз. (2) Симуляция терезесинде күн жана кос сигналдарынын радиусун ондук жана формат катары белгилеңиз> Аналогдук (автоматтык). (3) Толкун формасын көрүү үчүн кичирейтүү туура.

3 -кадам: Файлдар тиркелди

(1) cordic_v4.vhd - Дизайн. (2) testb.vhd - Дизайн үчүн сыноо стенди.

(3) Кантип бурчтук киргизүүлөрдү мажбурлоо жана экилик жыйынтыктарды айландыруу боюнча документ.

Жаңыртуу: БУЛ ФАЙЛДАР ОБСЕЛЕТ ЖАНА БИР КӨРСӨТҮЛБӨЙТ. КИЙИНКИ КАДАМДАН ФАЙЛДАРДЫ КОЛДОНУҢУЗ

4 -кадам: Mini -Cordic IP Core - 16 Bit

Жогорудагы ишке ашыруунун чектөөсү- жай, төмөнкү саат жыштыгында, анткени бир сааттык циклде эсептөөлөрдү жүргүзүү. Mini-Cordic IP Core- 16 Bit

- Критикалык жолдор иштөөнү жакшыртуу үчүн бир нече циклге бөлүштүрүлгөн.- Тезирээк- FPGA далилденген дизайн 100 МГцке чейин синтезделген. мурунку. Testbench:

0дон 360 градуска чейин бурчтук киргизүүлөр толугу менен автоматташтырылган

Тиркелген файлдар: 1) мини кордик негизги vhdl файлы2) мини кордикалык тест столу 3) Mini Cordic IP Core колдонмосу 4) бурчтарды мажбурлоо жана натыйжаларды айландыруу боюнча документ

Бардык суроолор боюнча, мени менен байланышуудан тартынба:

Mitu Raj

мени ээрчиңиз:

почта: iammituraj@gmail.com

### Бардык жүктөөлөр: 325 01-05-2021 чейин ###

### Код акыркы өзгөртүлгөн: июль-07-2020 ###

Сунушталууда:

Өзүн тең салмактоочу робот - PID башкаруу алгоритми: 3 кадам

Өзүн -өзү теңдештирүүчү робот - PID Control Algorithm: Бул долбоор ойлонулган, анткени мен Control Algorithms жана PIDтин функционалдык циклдерин кантип эффективдүү ишке ашыруу жөнүндө көбүрөөк билүүгө кызыкчумун. Долбоор дагы эле өнүгүү стадиясында, анткени Bluetooth модулу дагы кошула элек

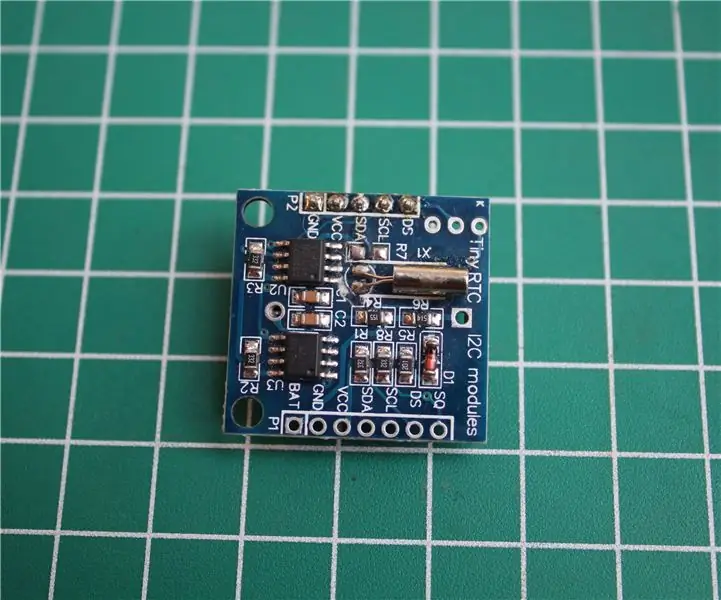

DS1307ди кантип колдонуу керек Arduino колдонуу: 7 кадам

DS1307ди кантип колдонуу керек Arduino колдонуу: DS1307 - бул чыныгы убакыт сааты IC (RTC). Бул IC убакыт маалыматтарды берүү үчүн колдонулат. Белгиленген убакыт секундадан, мүнөттөн, сааттардан, күндөрдөн, датадан, айдан жана жылдан башталат. Бул IC Crystal жана 3.6V батареялары сыяктуу кошумча тышкы компоненттерди талап кылат. Кристалл

Такта оюну Жасалма интеллект: Minimax алгоритми: 8 кадам

Стол оюну Жасалма интеллект: Минимакс алгоритми: Сиз шахматта же шашкиде ойногон компьютерлер кандайча жасалганын ойлонуп көрдүңүз беле? Бул Нускамадан ары караңыз, анткени ал Minimax Алгоритмин колдонуу менен жөнөкөй, бирок эффективдүү жасалма интеллектти (AI) кантип жасоону көрсөтөт! Муну колдонуу менен

Neopixel Ws2812 Rainbow LED жарыгы M5stick-C - менен Rainbowту Neopixel Ws2812де иштетүү M5stack M5stick Cди колдонуу Arduino IDEди колдонуу: 5 кадам

Neopixel Ws2812 Rainbow LED Glow with M5stick-C | Rainbow боюнча Neopixel Ws2812де чуркоо M5stack M5stick Cди колдонуу Arduino IDEди колдонуу: Салам балдар бул көрсөтмөлөрдө биз неопиксел ws2812 светодиоддорун же LED тилкесин же LED матрицасын же LED шакегин m5stack m5stick-C өнүктүрүү тактасы менен Arduino IDE менен колдонууну үйрөнөбүз жана биз жасайбыз. аны менен асан -үсөн үлгүсү

VHDL жана Basys3 тактасын колдонуу менен негизги секундомер: 9 кадам

VHDL жана Basys3 тактасын колдонуу менен негизги секундомер: Негизги VHDL жана Basys 3 тактасын колдонуу менен секундомерди кантип куруу керектиги боюнча инструкцияга кош келиңиз. Биз сиздер менен долбоорубузду бөлүшүүгө кубанычтабыз! Бул 2016 -жылдын күзүндө Cal Poly, SLOдогу CPE 133 (Санариптик Дизайн) курсунун акыркы долбоору болчу. Биз курган долбоор